Pi Pico Rx:数字时代的矿石收音机?

Pi Pico Rx - 数字时代的矿石收音机?

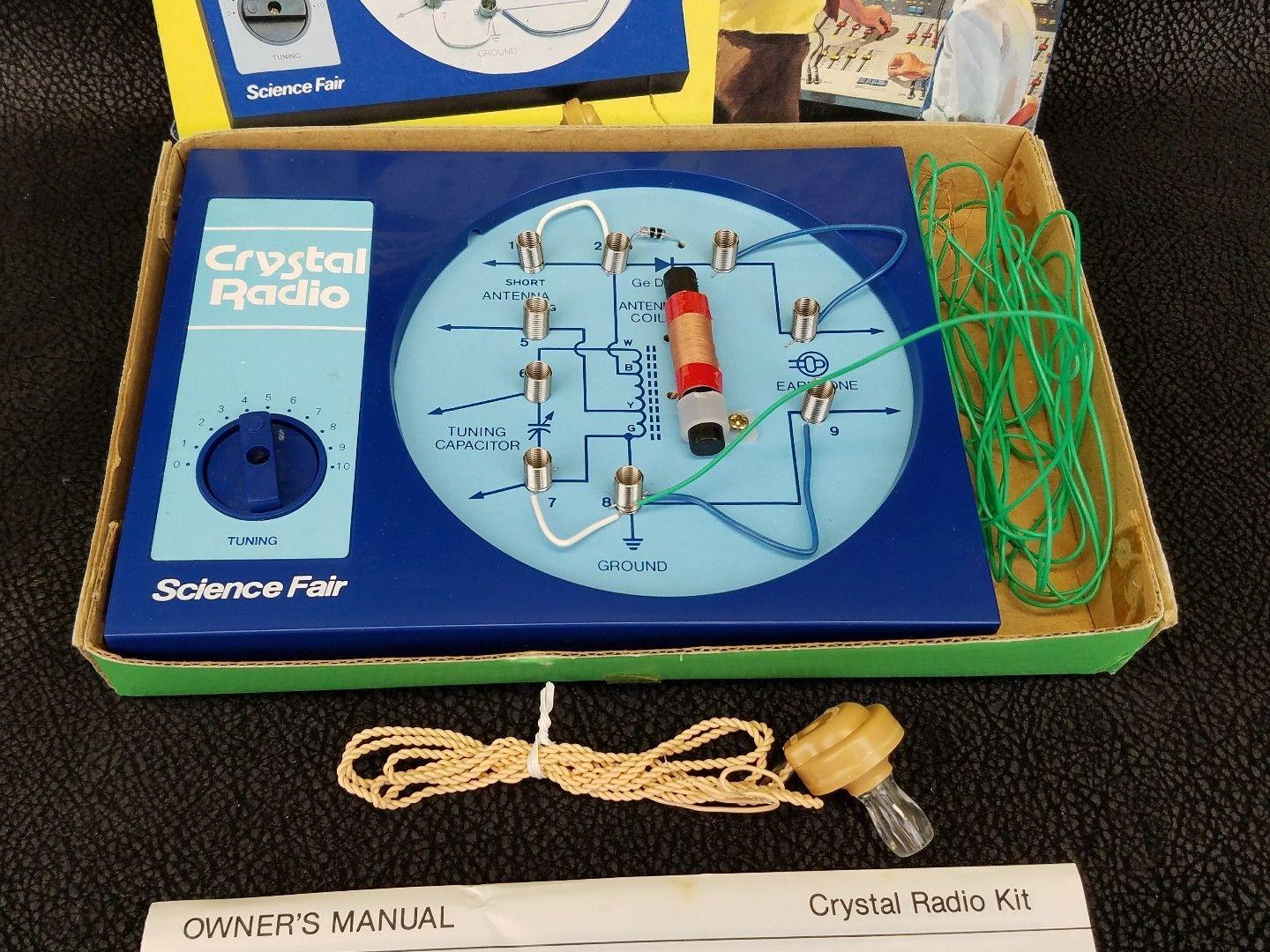

我第一次接触电子世界,就是通过矿石收音机,就像下面这个。

那时候,我从未想过自己也能制作收音机,所以没抱太大希望。但当我戴上耳机时,竟然听到了微弱的声音,这让我非常震惊。我简直不敢相信制作收音机如此简单,而且最棒的是,它不需要电池!这段小小的经历激发了我对电子学的兴趣。

那时候,我从未想过自己也能制作收音机,所以没抱太大希望。但当我戴上耳机时,竟然听到了微弱的声音,这让我非常震惊。我简直不敢相信制作收音机如此简单,而且最棒的是,它不需要电池!这段小小的经历激发了我对电子学的兴趣。

时代已经发生了翻天覆地的变化,今天,我们正处于电子爱好者的黄金时代。上世纪八十年代,我根本无法想象有一天我可以用零花钱买到一个计算能力在几十年前足以填满整个房间的设备。

我经常思考,我们如何才能再次捕捉到我第一次制作矿石收音机时所感受到的那种敬畏和兴奋之情。创造一些简单却引人入胜的东西是否仍然可能?

Pi Pico Rx 也许就是这个问题的答案。虽然它可能不如矿石收音机那样直接,但 Pi Pico Rx 提供了一个非常简单的解决方案。只需一个 Raspberry Pi Pico,一个模拟开关和一个运算放大器,我们就能够构建一个功能强大的 SDR 接收器,覆盖 LW、MW 和 SW 波段,并接收来自地球另一端发送的信号。想到这,我年轻时的自己一定会印象深刻!

如果您对一个更简单的版本感兴趣,该版本可以使用大部分通孔元件在面包板上构建,请查看面包板版本 这里。

功能特点

- 0 - 30MHz 覆盖范围

- 250kHz 带宽 SDR 接收器

- CW/SSB/AM/FM 接收

- OLED 显示屏

- 简单频谱显示

- 耳机/扬声器

- 500 个通用存储

- 使用 3 节 AAA 电池供电

- 低于 50mA 的电流消耗

Pi Pico Rx

Pi Pico Rx 是一款基于 Raspberry Pi Pico 的极简 SDR 接收器。 该设计使用由 Dan Tayloe 推广的 “Tayloe” 正交采样检测器 (QSD)。 并应用于 许多 HF SDR 无线电设计中。 这种简单的设计允许使用廉价的模拟开关来实现高质量的混频器。

正交振荡器使用 RP2040 的 PIO 功能生成。 这消除了使用外部可编程振荡器的需要。 在不对设备进行超频的情况下,它支持高达 30MHz 左右的频率,方便地覆盖了 LW、MW 和 SW 波段。

正交振荡器使用 RP2040 的 PIO 功能生成。 这消除了使用外部可编程振荡器的需要。 在不对设备进行超频的情况下,它支持高达 30MHz 左右的频率,方便地覆盖了 LW、MW 和 SW 波段。

来自 QSD 的 IQ 输出使用高速、低噪声运算放大器进行放大。 I 和 Q 通道由内置 ADC 采样,该 ADC 提供 250kHz 的带宽。 双核 ARM Cortex M0 处理器实现数字信号处理算法,解调 AM、FM、SSB 和 CW 以产生音频输出。

音频输出通过 PWM,然后通过低通滤波器提供。 起初,我使用 LM386 音频放大器,但后来发现,使用合适的限流电阻器,IO 引脚可以轻松地直接驱动一对耳机甚至小型扬声器。

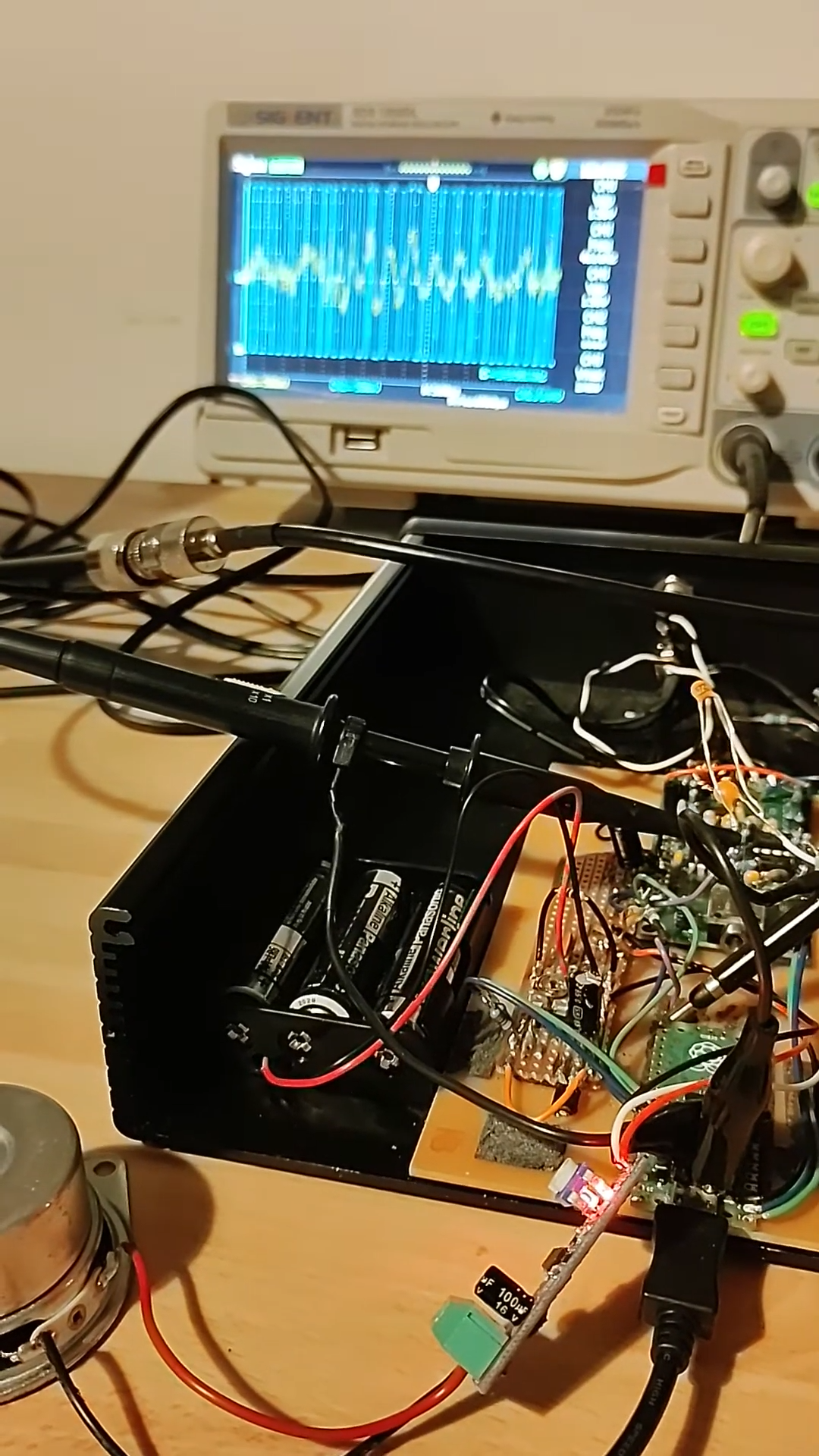

一个临时搭建的原型证明,可以使用 Pi Pico、模拟开关、运算放大器和一些分立元件来构建 HF SDR 接收器。

其他 SDR 接收器

这绝不是一个新想法,市面上有很多 SDR 设计。 一些使用 PC 声卡,另一些使用内置 CPU 进行 SDR。 uSDX 项目甚至使用 8 位微处理器进行 DSP 处理! 我列出了一些启发我的其他项目的链接。 这些项目中的每一个都引入了新的想法和创新。 我希望 Pi Pico Rx 已经引入了一些它自己的进化发展,可能会启发其他人的设计。

- softrock SDR

- QRP Labs

- mcHF

- elecraft KX3

- usdx

- (tr)uSDX

- uSDR-pico

- compact-si5351-based-sdr

- qex

- Teensy-Convolutional SDR

秉承知识共享的精神,我尝试在本 wiki 中描述硬件和软件的更精细的细节,从 Pi Pico Rx 引入的我在其他设计中从未见过的新功能概述开始。

使用循环 ADC 采样 IQ 数据

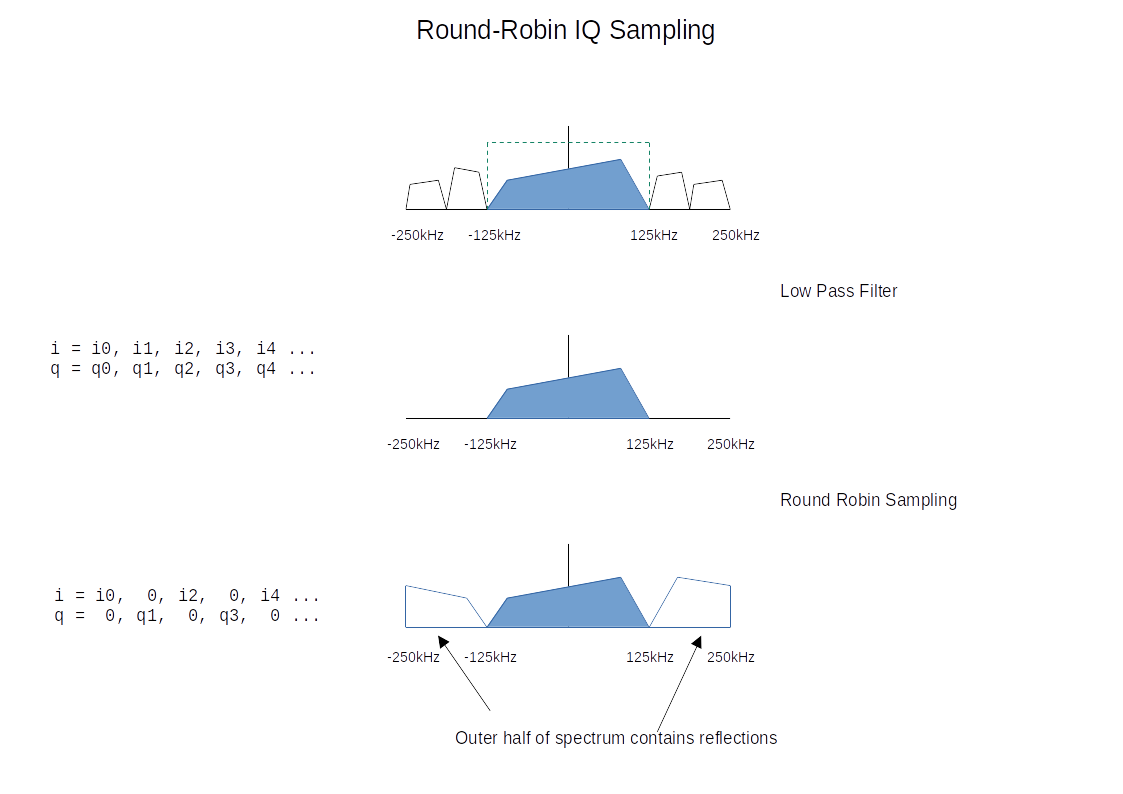

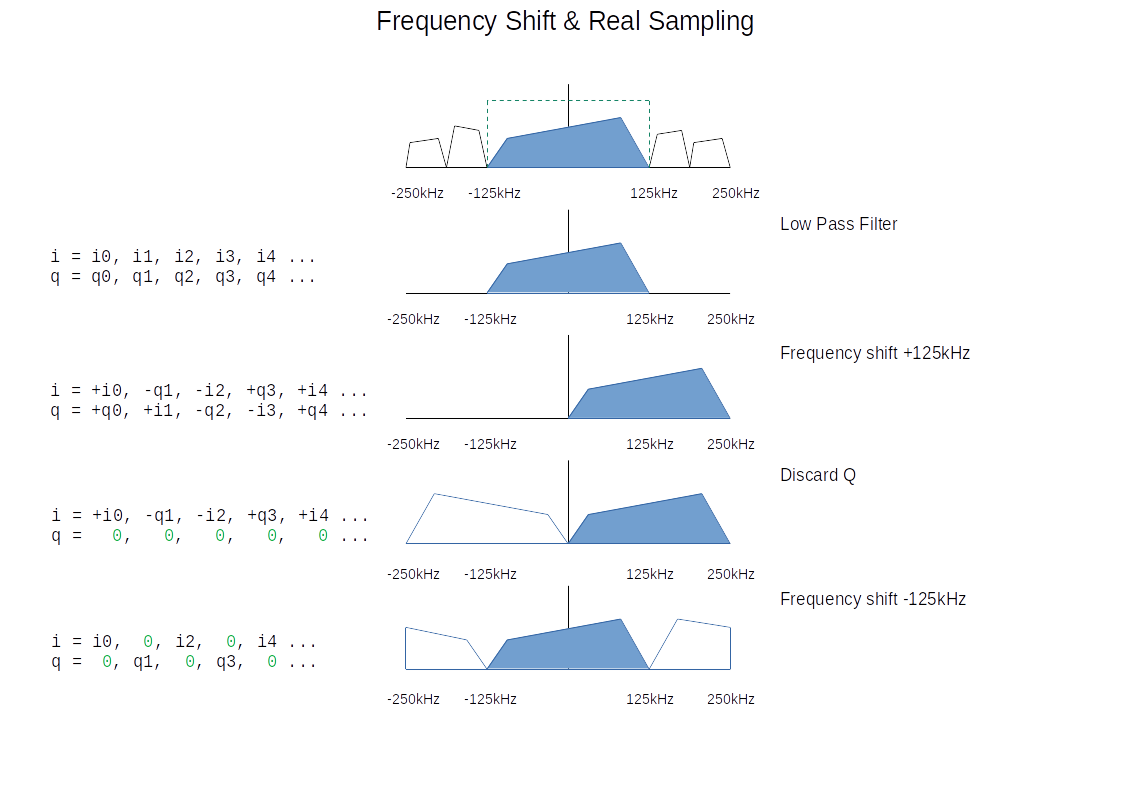

我面临的挑战之一是使用一次只能采样一个通道的 ADC 采样 IQ 信号。 它可以配置为循环模式,交替采样 I 和 Q。 我曾担心这可能会在 I 和 Q 通道之间产生相位不平衡。 我不必担心,事实证明,有一种简单的方法可以通过以 500kSample/s 交替采样 I 和 Q 来恢复具有 250kHz 带宽的复杂信号。

诀窍是对 I 和 Q 数据进行低通滤波,从而留下 -125kHz 到 125kHz 的 250kHz 带宽。 QSD 检测器本身形成一个低通滤波器,因此可以通过在运算放大器中选择合适的电容器值来轻松实现。 ADC 配置为交替采样 I 和 Q(从 I 开始)。 在软件中,“缺失”值可以用零代替。

这会产生一个采样率为 500KS/s 的复杂信号。 频谱的中心一半,从 -125kHz 到 125kHz,包含我们想要的频谱。 频谱的外部一半,从 -250kHz 到 -125kHz 和 125kHz 到 250kHz,包含中心一半的反射。 要恢复原始频谱,我们只需要对信号进行低通滤波,以便我们保留中心部分。 然后我们可以将采样率降低到 250kHz。 在我们的应用中,我们只滤除包含感兴趣信号的频谱的一小部分,我们不需要采取任何其他步骤来消除反射。

这会产生一个采样率为 500KS/s 的复杂信号。 频谱的中心一半,从 -125kHz 到 125kHz,包含我们想要的频谱。 频谱的外部一半,从 -250kHz 到 -125kHz 和 125kHz 到 250kHz,包含中心一半的反射。 要恢复原始频谱,我们只需要对信号进行低通滤波,以便我们保留中心部分。 然后我们可以将采样率降低到 250kHz。 在我们的应用中,我们只滤除包含感兴趣信号的频谱的一小部分,我们不需要采取任何其他步骤来消除反射。

为什么会这样?

为了理解为什么会这样,它有助于思考我们如何可以将信号转换为实数(而不是复数 IQ)信号,并使用单通道 ADC 对其进行采样。 这是我最初考虑采取的方法之一。 直到我解决了这个问题,我才意识到有一种更简单的方法。 这是我的思考过程。

为了满足 Nyquist,我们需要过滤复杂数据,以便我们所有的信号都位于 -125kHz 和 125kHz 之间。 然后我们可以将数据向上移动 125kHz,以便我们的信号位于 0 和 250kHz 之间。 频移是 500KSample/秒采样率的 1/4。 频移 Fs/4 可以通过在每个样本中将信号旋转 1/4 圈来实现。 这不需要任何乘法,只需要取反。

为了满足 Nyquist,我们需要过滤复杂数据,以便我们所有的信号都位于 -125kHz 和 125kHz 之间。 然后我们可以将数据向上移动 125kHz,以便我们的信号位于 0 和 250kHz 之间。 频移是 500KSample/秒采样率的 1/4。 频移 Fs/4 可以通过在每个样本中将信号旋转 1/4 圈来实现。 这不需要任何乘法,只需要取反。

由于我们的信号现在只包含正频率,因此信号的虚部 (Q) 不包含任何有用的信息,我们可以将其丢弃。 仅包含实数值 (I) 的信号具有对称频谱,丢弃虚部样本会引入正频率信号的负频率反射。

现在可以使用单通道 ADC 以 500kSamples/s 的速度对实数信号进行采样。 频移可以在硬件中使用简单的混频器来实现,但我们只需要交替的 I 和 Q 样本,因此我们可以使用循环 ADC 来捕获交替的 I 和 Q 样本,并在软件中实现混频器,在必要时对 I 和 Q 进行取反。

一旦我们在软件中有了实数信号,我们可能希望将实数信号转换回复数信号。 我们可以使用 Hilbert 变换,这将滤除负频率,留下一个具有非对称频谱的复数信号,其中仅包含 0 到 250kHz 的正频率。

另一种方法是将频率向下移动 125kHz,留下原始频谱,从 -125kHz 到 125kHz,现在在频谱的外部一半有反射。 这些可以使用低通滤波器消除。 我们可以采用相同的方法来处理 Fs/4 频移,这次在相反的方向上将每个样本旋转 1/4 圈。

检查生成的样本,我们可以看到向下频移已抵消了我们在向上频移期间执行的取反,从而使我们获得了最初捕获的交替 I/Q 样本。

方便的是,事实证明,从循环 ADC 捕获的交替 IQ 样本是完全捕获频谱中心一半所需的唯一样本。 “缺失”样本仅有助于我们已经过滤掉的频谱的外部部分。

使用 PIO 创建正交振荡器

pi pico 基于 RP2040 微控制器。 PIO 是 RP2040 的一项新颖功能。 可编程状态机(如小型微处理器)可以配置为从软件卸载 IO 功能。 配置 PIO 状态机以在 2 个 IO 引脚上输出正交振荡器非常简单。 配置完成后,振荡器自主运行,无需软件干预,也不会对 CPU 造成任何进一步的负载。

PIO 程序非常简单:

.program nco

set pins, 0

set pins, 1 ; Drive pin low

set pins, 3 ; Drive pin high

set pins, 2 ; Drive pin low

NCO 的频率可以使用 PIO 时钟分频器进行编程。 它具有一个 16 位整数和一个 8 位小数部分。 输入时钟为 125MHz,NCO 可以编程为从几百 Hz 到略高于 30MHz。 非常适合 LW/MW/SW 接收器。

在低频率下,可以实现良好的分辨率,但在高频率下,步长可能超过 100kHz。 但是,在 250kHz 的带宽下,这仍然足以提供整个频率范围的连续覆盖。 为了补偿振荡器中粗糙的频率分辨率,在软件中实现了一个高分辨率频移器。 (32 位相位累加器具有略高于 0.0001 Hz 的理论分辨率,这应该足够了。)

硬件设计

硬件的设计目标是使设计尽可能简单和廉价,同时不会过多地影响性能。 我设计了一个 PCB,它扩展了基本概念,包括一个前置放大器和一组低通滤波器。 要查看详细信息,您可以查看 pdf 格式的完整原理图,但我将在此处介绍一些详细信息。

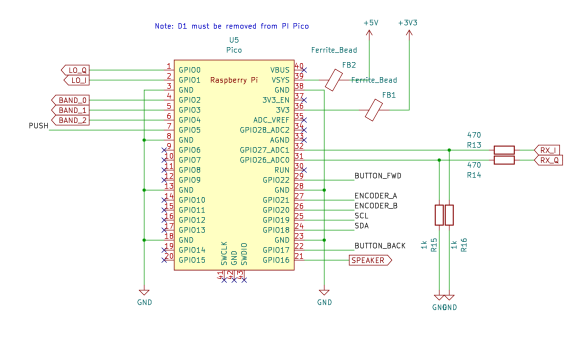

Raspberry Pi Pico

接收器的核心是 Raspberry Pi Pico。 板载 ADC 以 500kSamples/s 的速度采样,为我们提供 250kHz 的带宽。 12 位 ADC 的理论动态范围为 72 dB,但实际上不会那么好。 SSB 信号只需要 2.5kHz 的带宽。 我们可以用我们多余的带宽来换取增加的动态范围,从而提高整体灵敏度。 100 的过采样率为我们提供了额外的 20dB,相当于增加了 3 个额外的位。 这给出了 SSB 模式下 92dB 的理论动态范围。 ADC 的输入范围为 0 到 3.3V。 在没有放大的情况下,这代表 -78 dBm 到 14 dBm 的范围。

Raspberry Pi Pico 具有板载开关模式稳压器,允许 Pico 轻松地由电池供电。 此设计使用 3xAAA 电池。 可以向 pi pico 添加额外的外部组件,以允许设备由电池或 USB 电源供电。 此设计主要旨在作为便携式独立无线电,USB 连接提供编程闪存的能力。 为了避免添加额外的组件,我选择从 pico 中删除 D1。 这可以防止 USB 电源和电池之间发生争用。

Raspberry Pi Pico 具有板载开关模式稳压器,允许 Pico 轻松地由电池供电。 此设计使用 3xAAA 电池。 可以向 pi pico 添加额外的外部组件,以允许设备由电池或 USB 电源供电。 此设计主要旨在作为便携式独立无线电,USB 连接提供编程闪存的能力。 为了避免添加额外的组件,我选择从 pico 中删除 D1。 这可以防止 USB 电源和电池之间发生争用。

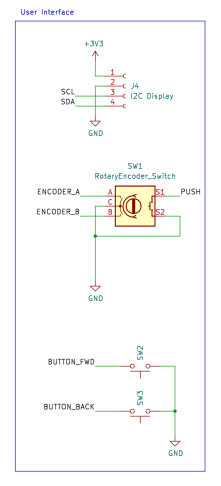

用户界面

用户界面没有什么特别之处。 128x64 OLED 显示屏使用基于 ssd1306 的 I2C 接口。 这些天来,这些接口非常普遍,并且已经取代 HD44780 作为首选的廉价/简单显示屏。 I2C 接口肯定有助于减少引脚数。 成本是一个关键驱动因素,我可以用一对按钮替换旋转编码器以节省成本,但我认为这将太过分了。 如果没有适当的调谐旋钮,它就不会像无线电。 理想情况下,我希望使用更紧凑的东西,安装在一个边缘上的基于拇指轮的旋转编码器将是理想的。 虽然似乎有一些,但似乎很难找到。 这个 定向导航滚动轮也引起了我的注意,但最终,成本胜出,我选择了一个标准编码器。

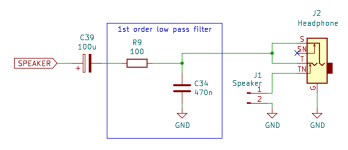

PWM 音频

起初,我考虑使用 LM386(或类似)音频放大器来驱动耳机或小型扬声器。 事实证明,PWM 完全能够直接驱动耳机或小型扬声器。 一个 100uF 电容器阻断 DC,电容越大,DC 响应越好,但在这种应用中,100uF 可能有点过头了。 RP2040 的最大驱动强度为 12mA。 100 欧姆电阻器用作限流电阻器和 RC 低通滤波器的一半。 峰值电压为 1.65v,假设内部电阻约为 40 欧姆,则流入 32 欧姆负载的最大电流为 1.65/(100+40+32) = 9.5mA,流入 8 欧姆负载的最大电流为 1.65/(100+40+8) = 11.1mA。

如果需要更好的扬声器,则 TPA2012 看起来是 LM386 的理想现代替代品,非常适合电池供电的应用。 该输出也适用于 PC 扬声器,但请注意驱动电平明显高于通常的 100mV pk-pk。

如果需要更好的扬声器,则 TPA2012 看起来是 LM386 的理想现代替代品,非常适合电池供电的应用。 该输出也适用于 PC 扬声器,但请注意驱动电平明显高于通常的 100mV pk-pk。

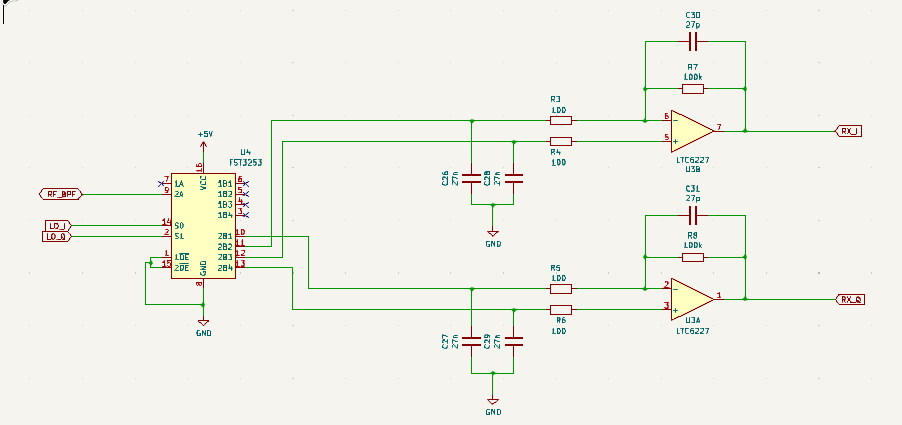

QSD 检测器 (Tayloe 检测器)

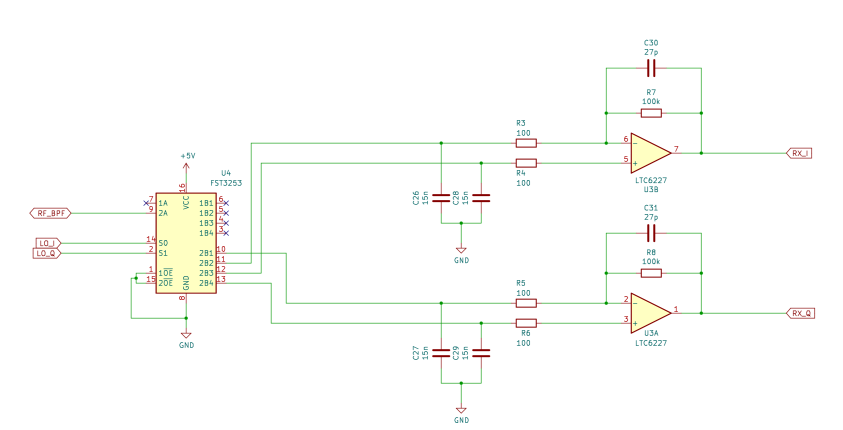

该设计使用由 Dan Tayloe 推广的 “Tayloe” 正交采样检测器 (QSD)。 它被用于许多 SDR 接收器,这是有充分理由的。 在此设计中,模拟开关的选择输入由 Raspberry Pi Pico 直接驱动,RP2040 的 PIO 功能能够在高达 30MHz 的频率下生成正交振荡器,而无需软件干预。 电阻值已选择为提供 1000 或 60 dB 的增益。 这给出了 QSD 输入端 -138 dBm 至 -46 dBm 的理论输入范围。 电容值已选择为提供约 60kHz 的截止频率和 120kHz 的带宽。 QSD 实际上充当抗混叠滤波器,因此一定程度的过采样有助于。 增益和带宽要求需要快速运算放大器。 LT6231 是此类 SDR 中的一个受欢迎的选择,因为它具有低噪声,并且它足够快,可以处理与大多数 SDR 相比,此设计中使用的更大带宽。 对于新设计,建议使用更新的 LTC6227 运算放大器,它甚至更好。

此设计的一个潜在弱点是 ADC 中可能发生混叠。 这对于使用声卡或音频 ADC 的 SDR 来说不是问题,它们通常包含非常好的抗混叠滤波器。 一个潜在的改进是包括一个有源低通滤波器。 这可以利用更基本(也更便宜)的运算放大器。 还可以通过级联几个更便宜的运算放大器来节省成本,在它们之间共享增益,每个阶段的增益带宽积可以低得多,并且后来的放大器的噪声性能不太关键。

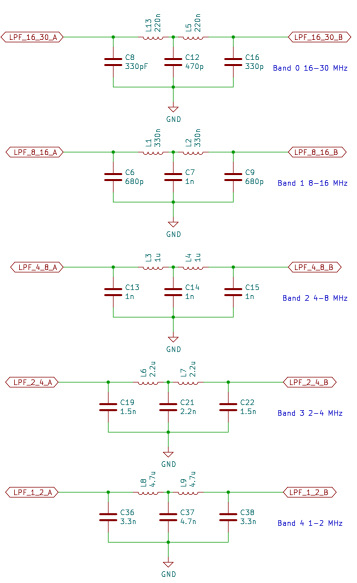

低通滤波器

Tayloe 检测器使用开关而不是模拟混频器,这给出了类似于将传入 RF 与方波混合的行为。 这意味着 QSD 对基波的奇次谐波处的信号敏感,其中最强的是调谐频率的 3 倍。 此设计采用低通滤波器来强烈衰减奇次谐波。 一组 5 个滤波器覆盖 1MHz 到 30MHz 的频率范围。 每个频段覆盖一个八度音阶,在 1MHz 到 2 MHz 频段中,2MHz 的截止频率衰减了可能在 3MHz 到 6MHz 之间的三次谐波。 随着频率的增加,频段的宽度可以加倍,因此 1MHz 到 30MHz 的范围可以用 5 个滤波器覆盖。 为了覆盖完整的 LW 和 MW 范围,我至少需要 3 个以上的滤波器,考虑到频谱这一部分中电台的数量有限,这似乎过多了,因此我决定只接受该范围内奇次谐波处发生干扰的可能性。 用户如果对这些频段感兴趣,没有理由不能添加一个额外的滤波器,甚至可以将其内置到磁环天线或铁氧体天线中。

有一些在线工具可以用来计算滤波器值,我使用了 这个。

有一些在线工具可以用来计算滤波器值,我使用了 这个。

在实践中,强大的本地 AM 电台会导致干扰,因为这些电台往往位于较低的频率,因此低通滤波器几乎无法衰减它们。 带通滤波器会提供更好的性能。 我发现安装外部 AM 带阻滤波器大大提高了 SW 频率范围内的性能。

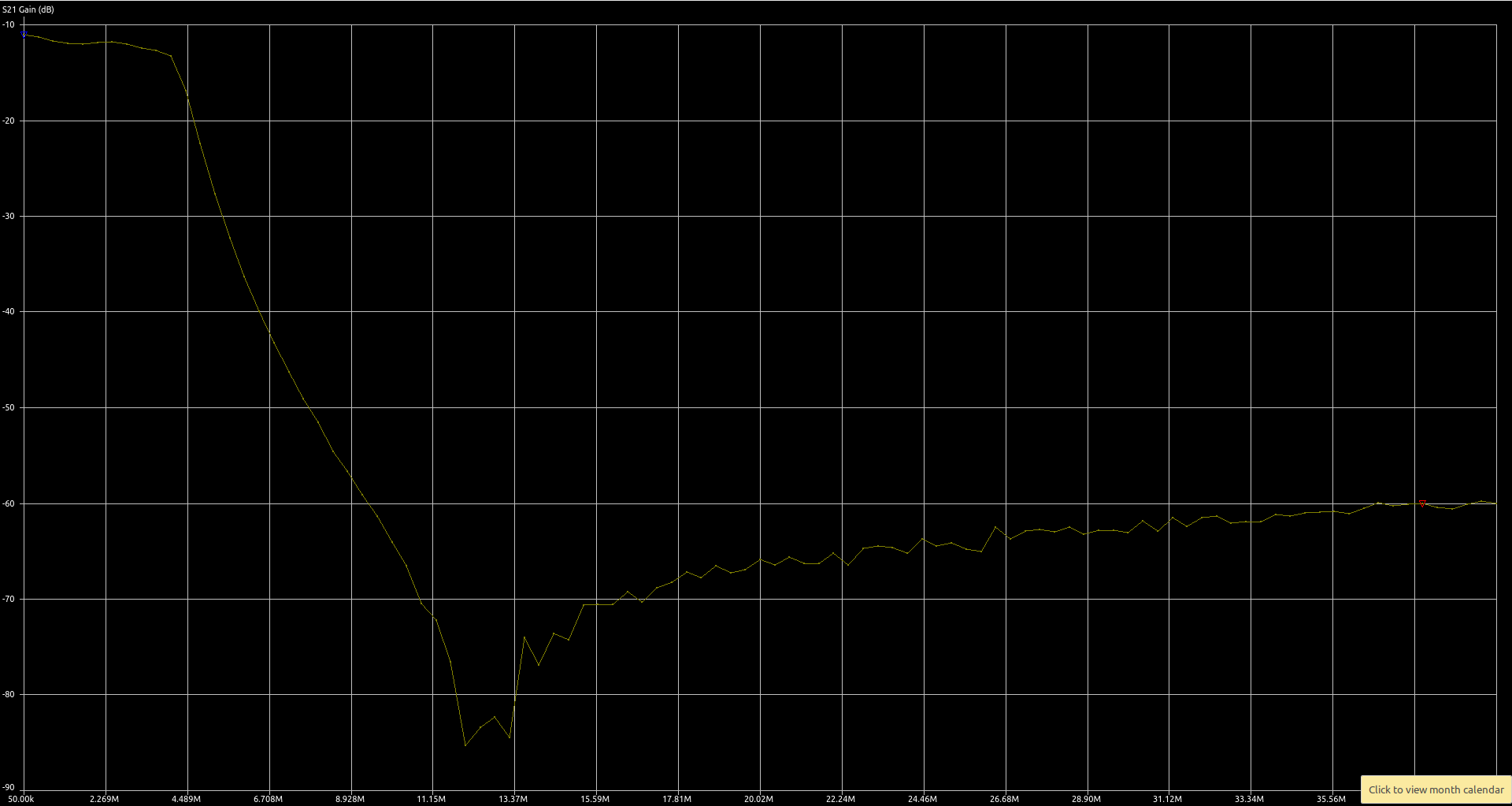

我使用 nanovna 测量了滤波器响应。 这消除了设计中的大量猜测。 我在部分组装 PCB 后直接连接到滤波器。

这个具有所需的 4MHz 截止频率,并且在阻带中具有超过 60dB 的衰减。 在通带中,插入损耗约为 10 dB。 这给出了大约 -128 dBm 到 -36 dBm 的理论功率范围。

这个具有所需的 4MHz 截止频率,并且在阻带中具有超过 60dB 的衰减。 在通带中,插入损耗约为 10 dB。 这给出了大约 -128 dBm 到 -36 dBm 的理论功率范围。

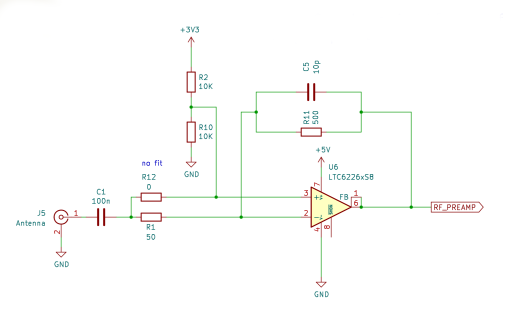

前置放大器

在 LW/MW/SW 频段中,存在高水平的大气噪声。 可以说,不需要前置放大器。 如果我们可以达到 -128 dBm 到 -36 dBm 的理论范围,这将为我们提供所需的所有灵敏度。 在实践中,ADC 具有约 20dB 的内部噪声。 略好于 -100dBm 的 MDS 可能是一个更现实的数字。

一个好的经验法则是,接收器应该能够“看到”天线噪声,以提供解析弱信号的最佳机会。 检查此问题的理想方法是,当连接天线时,查看噪声本底是否上升了约一个 s 点。

使用阁楼安装的线天线,我发现接收器足够灵敏。 但是,对于便携式使用,需要更紧凑的天线。 我在使用 youloop 天线时获得了良好的效果,但我需要添加一个低噪声放大器才能获得良好的效果。 我在原型中使用了典型的 20dB 基于 MMIC 的 LNA。 我考虑过使用像 MAR6 这样的 MMIC 放大器。 相反,我选择使用 LTC6226 运算放大器(QSD 中使用的 LTC6227 放大器的单放大器版本)。 这种低噪声放大器具有足够的 GBP,可在 30MHz 带宽上提供 20dB 的增益。 放大器使用具有 50 欧姆输入阻抗的反相配置。 反馈网络包括一个电容器和一个电阻器,以提供具有 30MHz 截止频率的低通滤波器行为。

使用 LTC6226 前置放大器,我可以使用 youloop 天线听到大量微弱的信号,但我现在发现强大的本地 AM 电台会使接收器过载,从而导致严重削波。 可能会调整前置放大器中的增益以找到更好的折衷方案,从而允许接收到大多数信号。 也许可以添加一个可切换的衰减器,以使接收器更通用。

使用 LTC6226 前置放大器,我可以使用 youloop 天线听到大量微弱的信号,但我现在发现强大的本地 AM 电台会使接收器过载,从而导致严重削波。 可能会调整前置放大器中的增益以找到更好的折衷方案,从而允许接收到大多数信号。 也许可以添加一个可切换的衰减器,以使接收器更通用。

外壳

外壳通常最终成为电子项目中最昂贵的组件之一。 但是,现在可以非常便宜地制造具有一系列颜色和对比丝网印刷的 PCB,它们可以精确地进行机械加工并且非常坚固。 简而言之,它们是理想的前(和后)面板。 我选择了一种 PCB 三明治式结构来构建一个廉价、坚固且外观相当智能的设备。

软件设计

Raspberry Pi Pico 包含一个双核处理器。 第一个内核处理用户界面、驱动显示屏、旋转编码器、按钮和闪存接口。 第二个内核专门用于实现 DSP 功能。 这些内核使用控制和状态结构进行通信,这些结构受互斥锁保护。 控制和状态数据在两个内核之间定期传递。

ADC 接口

ADC 接口配置为循环模式。 两个 DMA 通道用于将 4000 个样本的块从 ADC 传输到内存。 选择 4000 个样本是相当随意的,当最坏情况下的执行时间明显长于平均值时,更长的块会提供额外的裕量(以额外的内存为代价)。 DMA 通道配置为使用 DMA 链接以乒乓方式进行。 当每个 DMA 通道完成时,另一个 DMA 通道会自动启动。 DMA 链接允许自主读取 ADC,而不会对 CPU 造成任何负载。

实时处理

当每个 DMA 传输完成时,都会调用 process_block function。 process_block 函数获取一个 I/Q 样本块并输出一个音频样本块。 在 500kSamples/s 的采样率下,这为我们提供了 8ms 的实时截止时间来处理每个块。 在 125MHz 的 CPU 频率下,这意味着我们每个块正好有 100 万个时钟周期。 完成工作后,计时器会测量空闲时间,直到下一个块完成。 CPU 利用率可以计算为 utilisation = (8ms - idle_time)/8ms,在开发过程中监控 CPU 利用率很有用,因此可以评估每次更改的影响。 process_block 函数是软件中唯一对时间要求严格的部分,软件的这一部分使用定点算术并从 RAM 运行,以最大限度地提高性能。 软件的其他部分不是特别关键,因此它从闪存运行并且可以自由使用浮点运算。

DC 消除

第一项任务是消除 DC,这可以通过对每个块中的样本进行平均来实现,平均值代表 DC 电平,然后从下一个块中减去该值。 事实证明,这比使用 DC 阻断滤波器稍快。 在 DSP 链中的这一点上,DC 消除过程并不是那么关键。 接收器使用低 IF,因此所需的信号始终与 DC 偏移几 kHz。 一旦我们对信号进行了频移,任何剩余的 DC 都会超出通带,并被抽取滤波器消除。 起初,我从原始(无符号 0 到 4095)ADC 样本中减去 2048,以提供一个有符号值(-2048 到 2047)。 事实证明,此过程是多余的,如果我们省略减法,DC 消除过程会将此视为额外的 DC 电平 2048 并无论如何将其消除。

频移

在可以对样本进行频移之前,我们需要将样本转换为复数格式。 循环 ADC 在 I 和 Q 样本之间交替,因此偶数编号的样本将为 I,奇数编号的样本将为 Q。 形成复数样本所需的“缺失”样本需要替换为零。

int16_ti=(idx&1^1)*raw_sample;//even samples contain i data

int16_tq=(idx&1)*raw_sample;//odd samples contain q data

由于 RP2040 可以在一个时钟周期内执行乘法,因此乘以样本 1 或 0 比使用三元 idx&1?raw_sample:0 语法选择样本更快。 这在其他平台上可能不成立。 一旦信号采用复数格式,我们就可以使用固定频率音调的复数乘法将所需信号频移到频谱中心。

频偏有两个组成部分,第一个是补偿正交振荡器的有限频率分辨率(我们想要的频率与我们获得的频率之间的差异)。 另一个组成部分是我们故意引入的低 IF 偏移,以将所需信号移离 DC。 在 DC 附近往往有很多由 LO 泄漏、市电嗡嗡声等引起的干扰。 应用频偏允许我们滤除此干扰。

我们需要创建一个复数音调来“消除”频偏。 我们无法足够快地计算 sin 和 cos 值以进行实时操作,因此我们计算一个包含 2048 个值的查找表,这些值代表一个完整周期。 通过对 sin 和 cos 值使用相同的查找表来节省一些内存,cos 通过将 pi/2 相移应用于索引从 sin 表计算得出。 这些值经过缩放,以提供 15 个分数位,其大小略小于 1,以便充分利用可用的 16 位,而不会导致溢出。

//pre-generate sin/cos lookup tables

floatscaling_factor=(1<<15)-1;

for(uint16_tidx=0;idx<2048;idx++)

{

sin_table[idx]=sin(2.0*M_PI*idx/2048.0)*scaling_factor;

}

对于每个样本,32 位相位累加样本的相位变化值(频率)。 缩放 32 位相位和频率值,使 0 到 (2^32)-1 代表范围 0 到(几乎)2*pi。 相位累加器的 11 个最高有效位用作查找表的索引。 尽管只有相位累加器的 11 位用于索引查找表,但相位以更高的分辨率进行累加。 截断 21 个最低有效位导致的舍入误差会导致短期相位抖动,但这往往会在以后的周期中得到补偿,从而在长期内为我们提供非常精确的平均频率。

constuint16_tphase_msbs=(phase>>21);

constint16_trotation_i=sin_table[(phase_msbss+512u)&0x7ff];//32 - 21 = 11MSBs

constint16_trotation_q=-sin_table[phase_msbs];

phase+=frequency;

然后可以使用复数乘法将音调应用于信号,从而将所需的信号移至频谱中心。 乘法结果现在具有需要消除的额外 15 个分数位。 截断会导致大约 1/2 和 LSB 的负偏置。 这在信号处理的后期可能会出现问题(特别是对于我们故意将 DC 移入音频范围的 CW 信号)。 我们可以在此处使用更好的舍入方法来消除偏置,但这需要在软件的关键部分占用大量额外的 CPU 周期。 一种更有效的方法是估计在处理的每个阶段引入的偏置,然后可以在一个地方补偿总偏置,在抽取后消除偏置会大大减少所需的周期数。

constint16_ti_shifted=(((int32_t)i*rotation_i)-((int32_t)q*rotation_q))>>15;

constint16_tq_shifted=(((int32_t)q*rotation_i)+((int32_t)i*rotation_q))>>15;

抽取

在这一点上,我们仍然以 500kSamples/s 的采样率工作,这远远超出了我们的需要。 我们尝试处理的最高带宽信号是带宽为 9kHz 的 FM 信号。 在此阶段,我们可以大幅降低采样率,这将使后期阶段的计算负载减少相同的因子。 在此设计中,循环 IQ 采样会在频谱的外部一半中引入图像。 这些图像也会在抽取过程中消除。

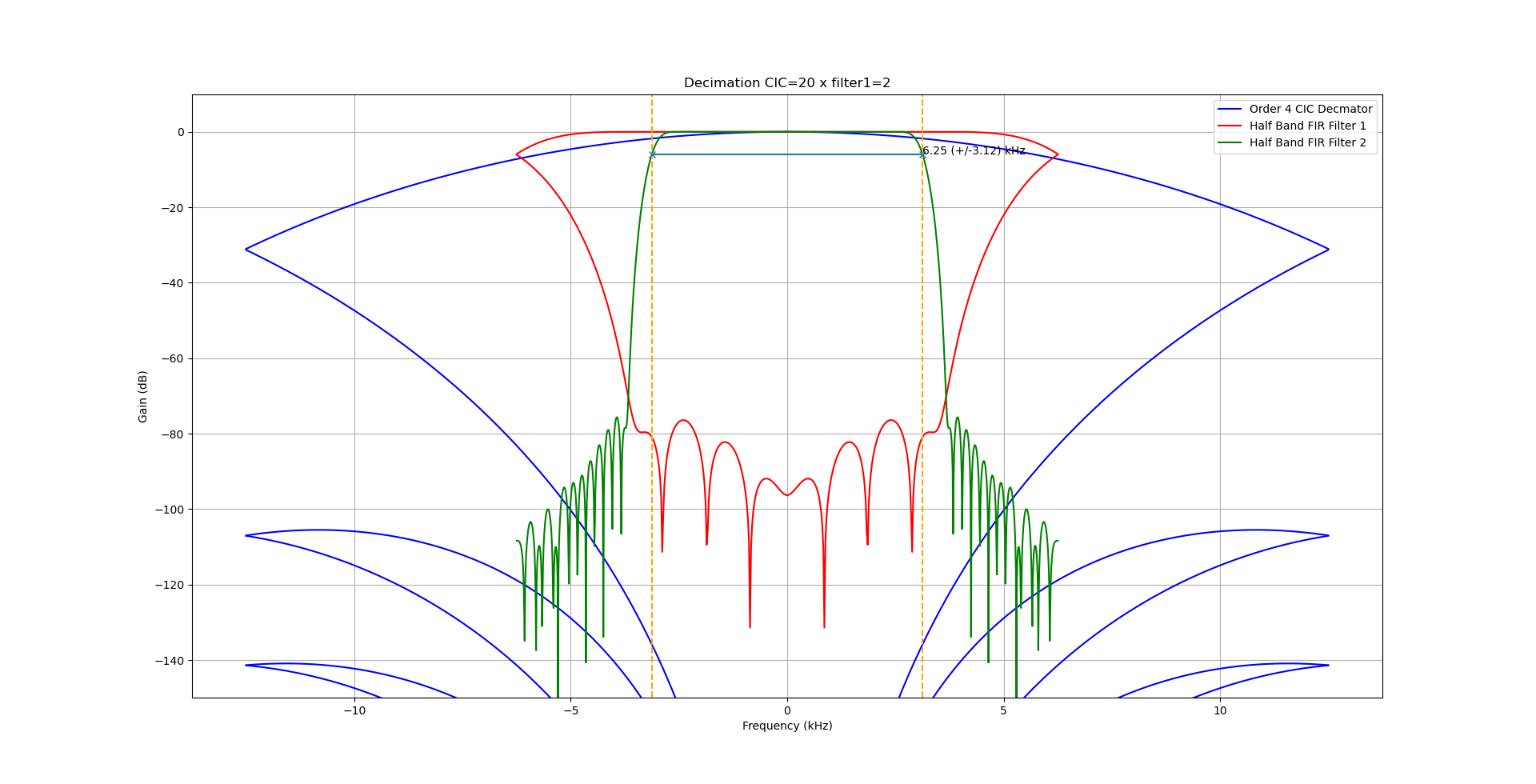

抽取是使用 CIC 和 半带 滤波器的组合实现的,以执行抽取,从而为我们留下一个狭窄的频谱。

CIC 是一种非常高效的滤波器设计,但它没有非常锋利的边缘,这会导致频谱边缘出现混叠。 这些混叠在使用第一个半带滤波器之前被消除,然后再抽取 2 倍。 第二个和最后一个半带滤波器消除了频带边缘剩余的任何混叠,最后一个半带滤波器是更高阶的滤波器,提供更清晰的边缘。 在最后阶段没有执行抽取,因此不会引入任何进一步的混叠。

CIC 是一种非常高效的滤波器设计,但它没有非常锋利的边缘,这会导致频谱边缘出现混叠。 这些混叠在使用第一个半带滤波器之前被消除,然后再抽取 2 倍。 第二个和最后一个半带滤波器消除了频带边缘剩余的任何混叠,最后一个半带滤波器是更高阶的滤波器,提供更清晰的边缘。 在最后阶段没有执行抽取,因此不会引入任何进一步的混叠。

在此设计中,根据模式调整抽取因子,从而导致不同的最终采样率和带宽。 这是一种非常简单有效的方法,可以改变最终滤波器的带宽。

| 模式 | CIC 抽取 | HBF 1 抽取 | 抽取后采样率 (Hz) | 抽取后带宽 (Hz) | |---|---|---|---|