低成本高性能 10 MHz - 15 GHz 矢量网络分析仪的设计

[正文内容]

低成本高性能 10 MHz - 15 GHz 矢量网络分析仪的设计

日期 2025-04-15

引言

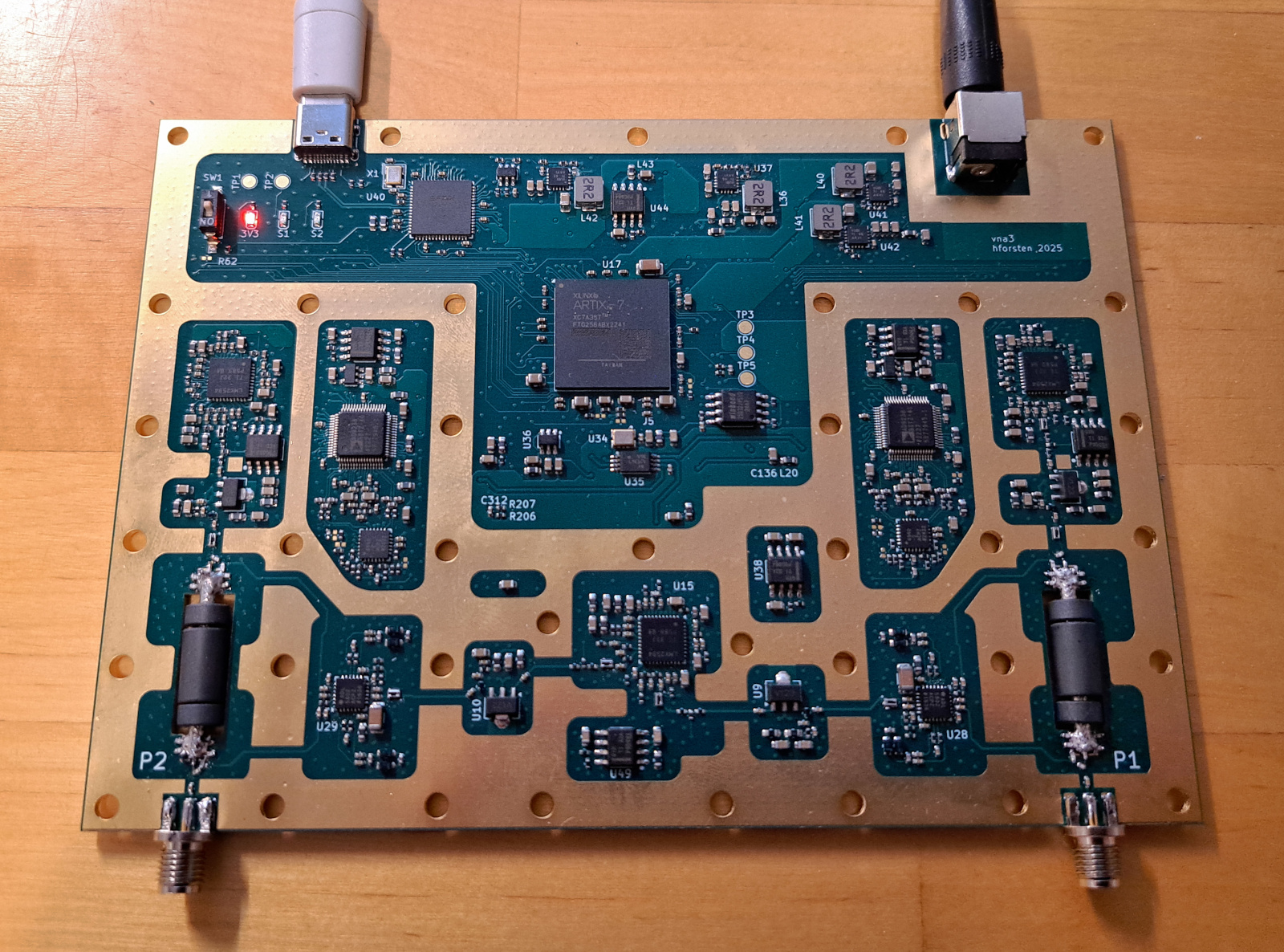

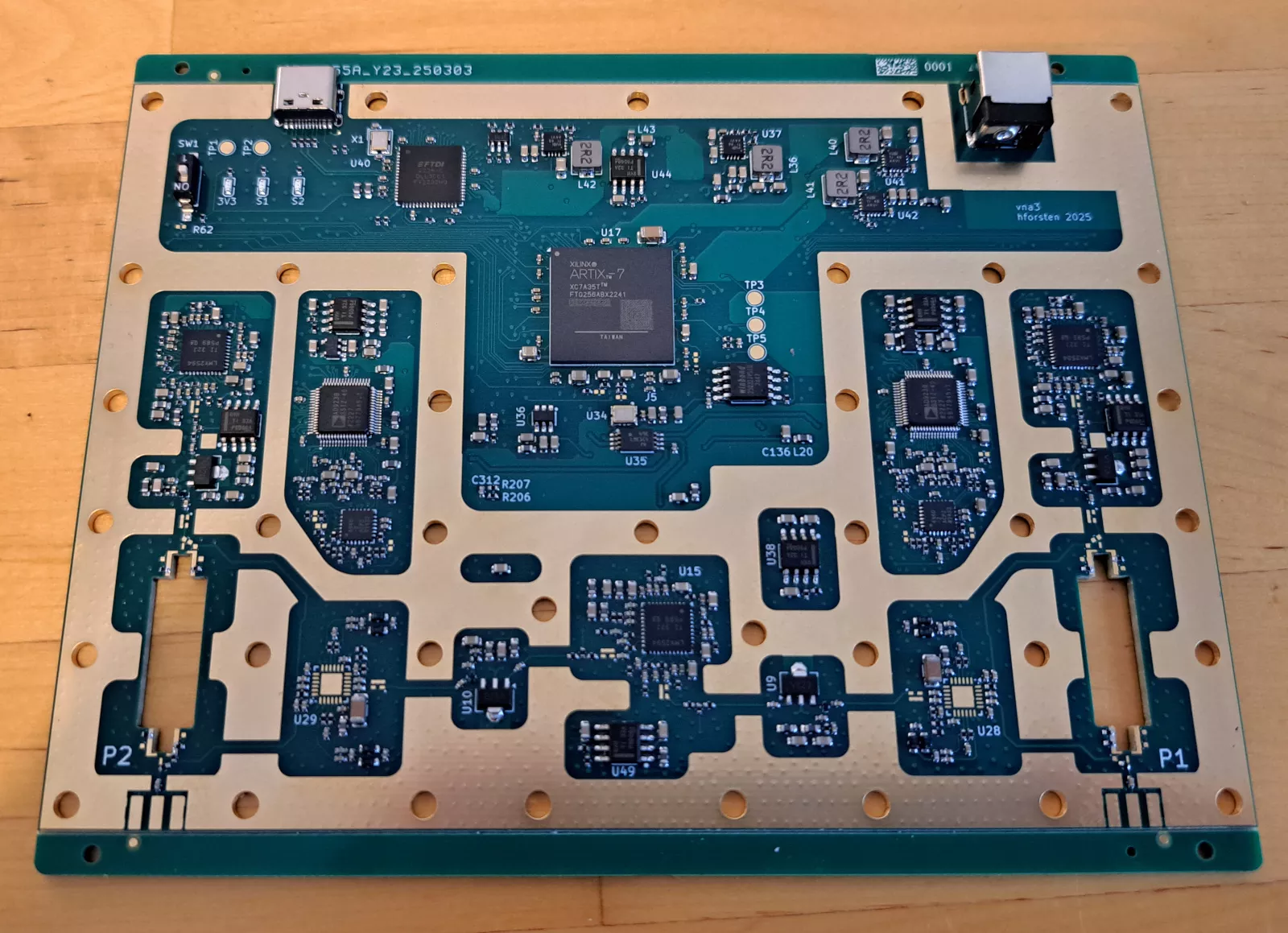

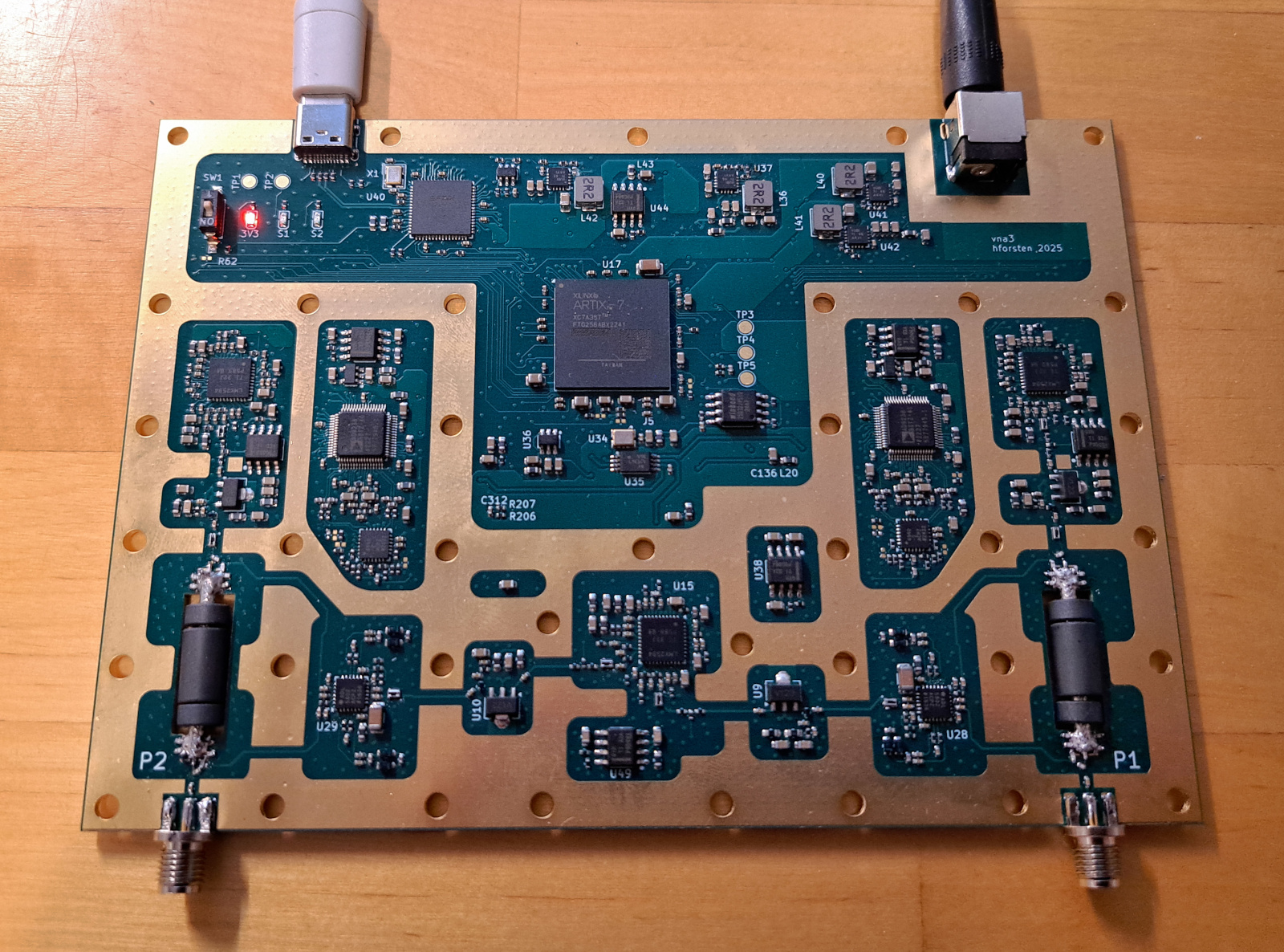

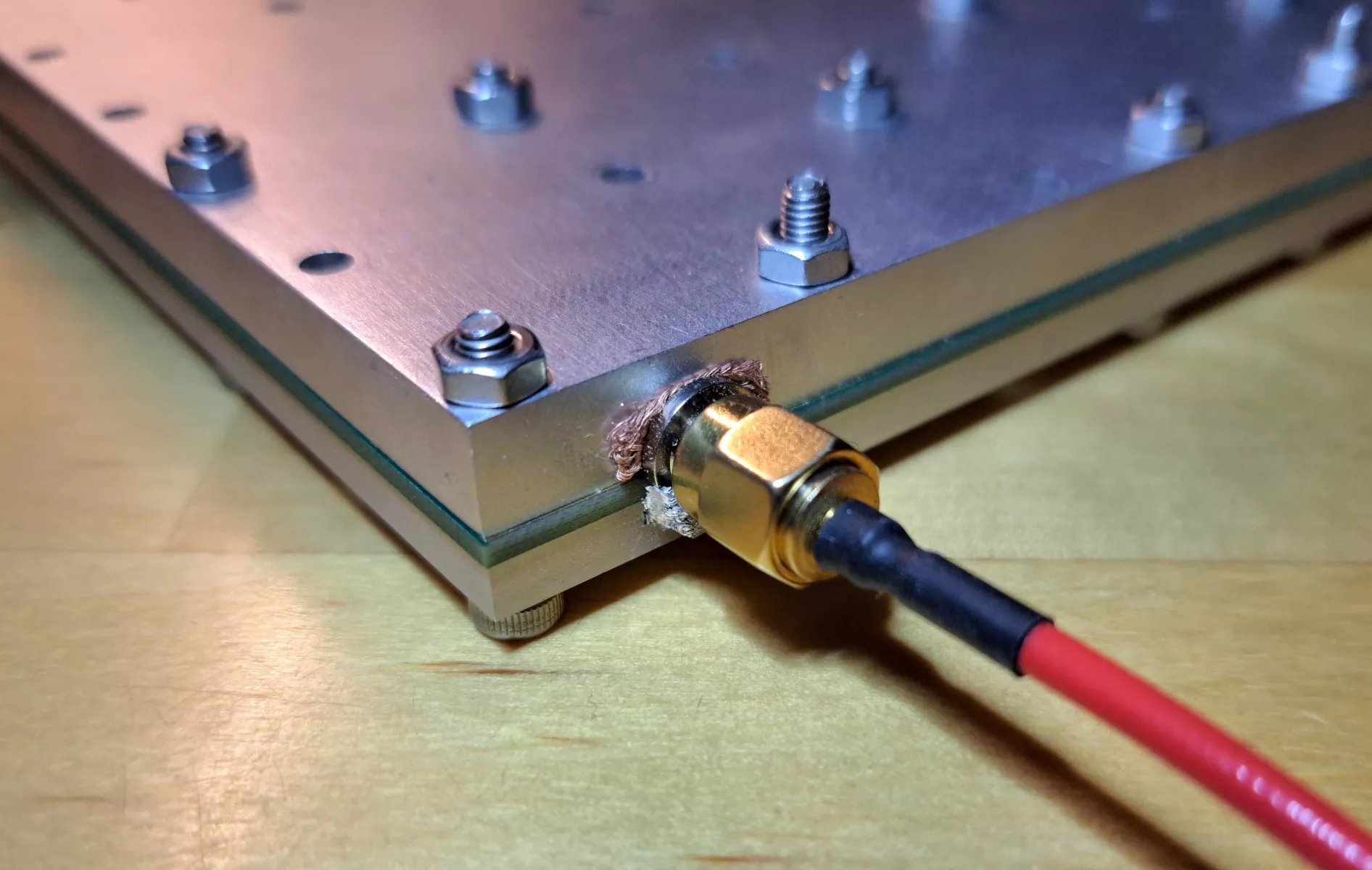

VNA PCB。

VNA PCB。

矢量网络分析仪(Vector network analyzer,VNA)是一种用于测量高频电气电路的散射参数的设备。S 参数描述了电路将多少功率反射回信号源,以及将信号衰减或放大到其他端口的程度。使用 S 参数是设计任何在 GHz 频率下运行的电子设备的重要组成部分。

这些设备并不便宜,特别是当工作频率增加时。工作在毫米波频率的高端 VNA 可能花费数十万美元,即使是经济实惠的低频设备也很昂贵。

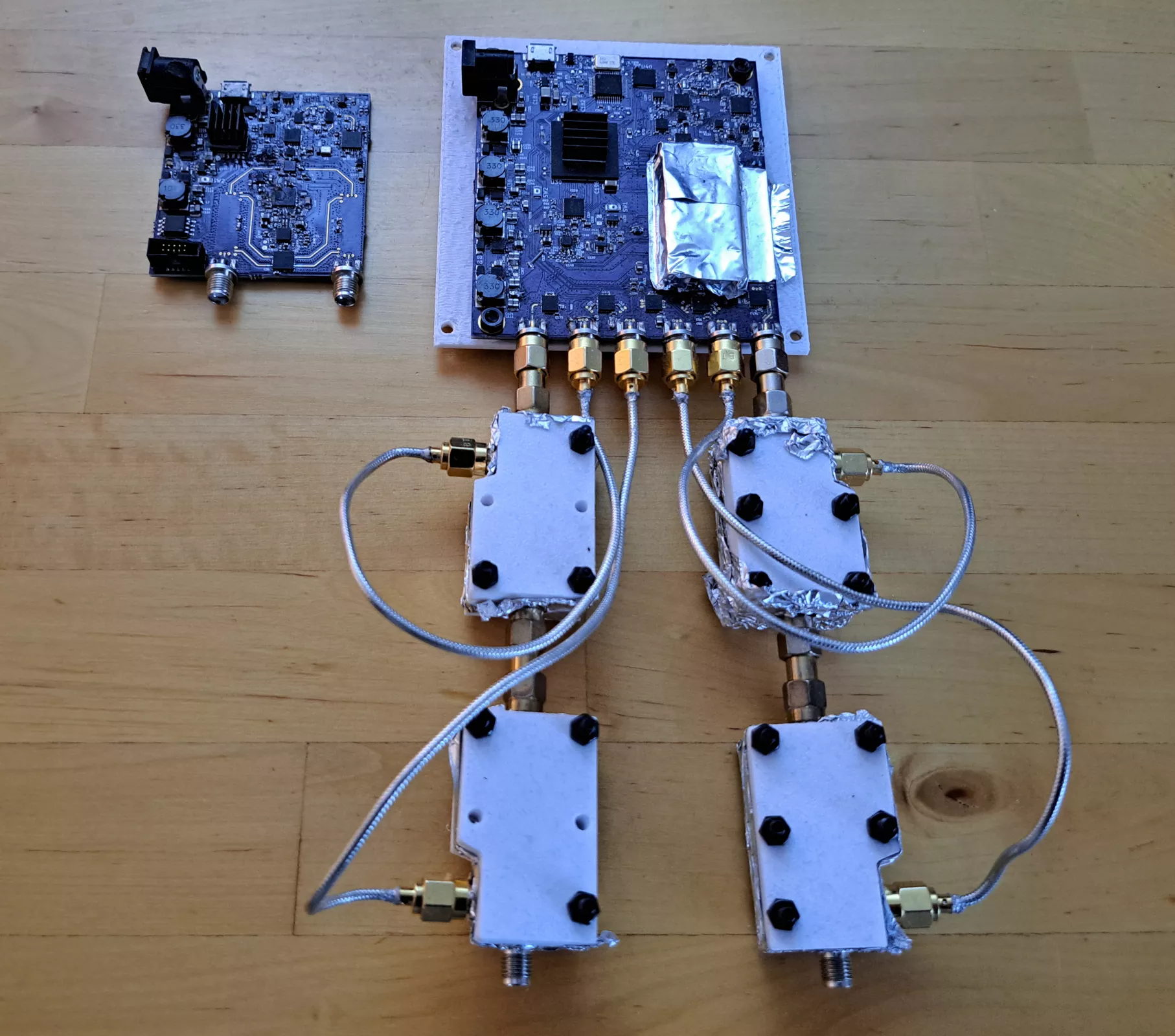

我之前自制的两个 VNA。

我之前自制的两个 VNA。

2016 年,我制作了我的第一个廉价的 10 MHz 至 6 GHz 双端口矢量网络分析仪。当时,没有廉价的 VNA 可用,我不得不自己设计一个。它虽然能用,但两个端口之间的泄漏很高,导致很大的测量误差,最终导致许多测量的精度不可用。第二年,我设计了改进版本,它具有更好的性能,并且实际上很有用。我一直将它用于我自己的项目,但最近,它开始显得有些局限,我想购买或制造一个更好的 VNA。我希望有更高的最大频率,最好是 >10 GHz,更好的测量精度和良好的端口间隔离。

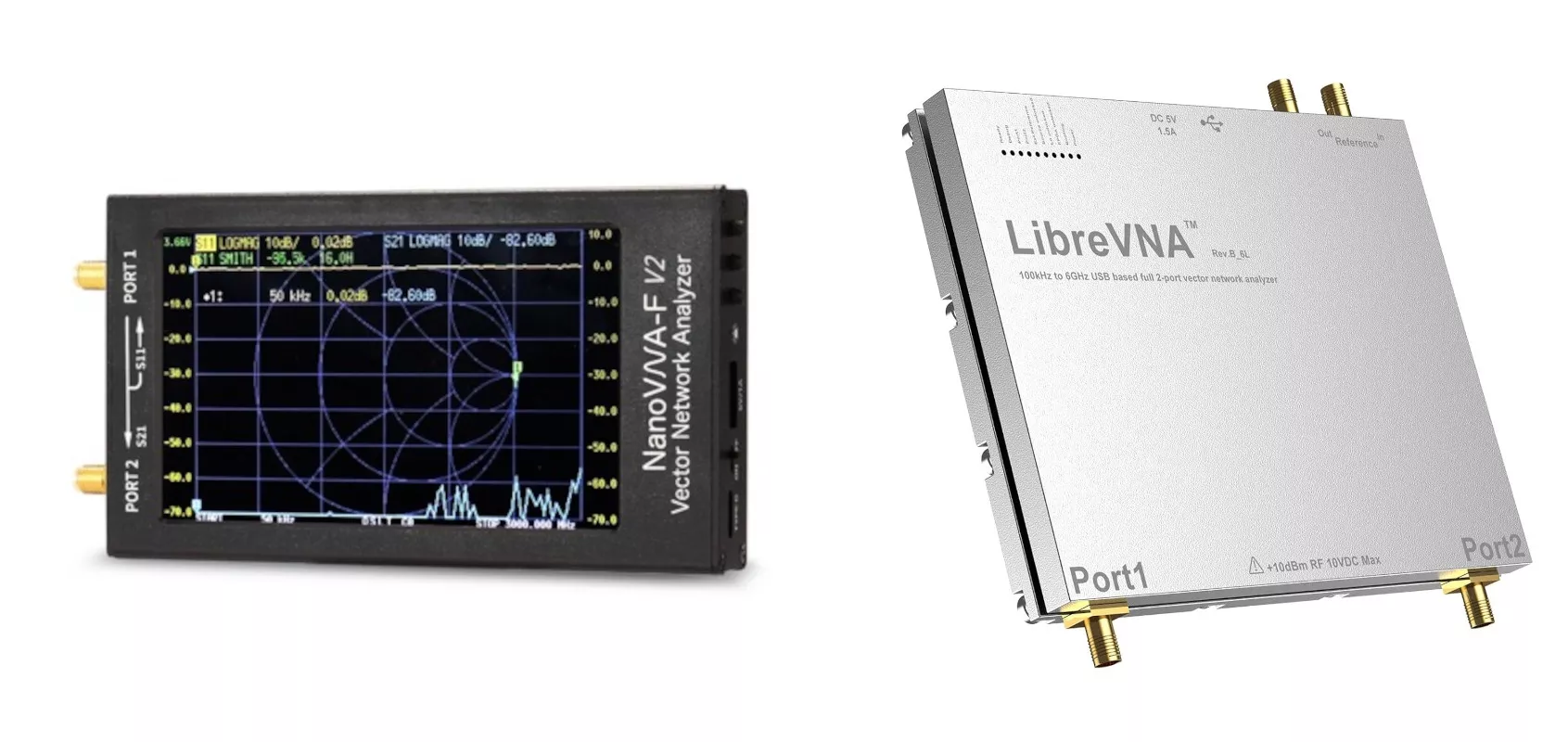

nanoVNA(左)和 LibreVNA(右)。

nanoVNA(左)和 LibreVNA(右)。

现在,有很多廉价的商用 VNA。最受欢迎的可能是 nanoVNA。它有几个不同的版本,但它们大多限制在 1 - 4 GHz 左右,这对我来说不够。它也是一个所谓的 1.5 接收器设计,只能测量 S11 和 S21,需要手动翻转被测设备才能完全测量双端口 S 参数。它并不比我已经拥有的更好。还有其他一些 1.5 接收器 VNA,有些更好,有些更差,但是 1.5 接收器架构太局限,并且会导致不准确的测量结果,不值得考虑。

更进一步的是 LibreVNA。它是一个 100 kHz 至 6 GHz 的双端口 VNA,部分基于我之前的 VNA 设计。它比我之前的 6 GHz VNA 具有更好的性能,但性能不如我想要的好。3 GHz 以上的泄漏非常高,这限制了测量精度。与 nanoVNA 不同,它是一个合适的双端口 VNA,可以测量双端口 S 参数,而无需手动翻转设备。但是,它是一个三接收器设计,而不是性能更好的四接收器设计。在端口开关之前有一个共享的参考接收器,用于测量输出信号,而不是每个端口都有两个单独的参考接收器。使用高级校准方法,例如 TRL 和 unknown thru,需要具有四个接收器的双端口 VNA。这些方法非常有用,因为它们放宽了对校准套件已知程度的要求,从而提高了测量精度,尤其是在使用低成本、不准确的校准套件时。

Keysight E5603 VNA。100 kHz 至 18 GHz 的选件的标价为 53,000 欧元,而且这甚至不是高端型号。

Keysight E5603 VNA。100 kHz 至 18 GHz 的选件的标价为 53,000 欧元,而且这甚至不是高端型号。

有性能更好的 VNA,非常适合我的要求,例如来自 Copper Mountain 或 Keysight 的 VNA,但即使是最便宜的 >10 GHz 的 VNA 也要超过一万美元。

我找不到满足我要求的廉价双端口 VNA,但是在稍微思考了一下后,我非常确定我可以制造自己的 VNA,即使考虑到小批量原型机较高的价格,它也比目前可用的任何其他廉价 VNA 具有更好的性能。

VNA 架构

典型的 VNA 由激励和本地振荡器信号源组成。信号源通过端口开关路由到一个端口,另一个端口端接为 50 欧姆。然后,信号通过定向耦合器,该定向耦合器对入射波和反射波进行采样。这些波与本地振荡器混合,以将其转换为可以使用 ADC 采样的低频信号。这些测量可用于计算反射波和传输波的幅度和相位。

这种架构的主要问题是端口开关。它需要在 VNA 的整个工作带宽上具有 >100 dB 的隔离度,这很难实现,需要将几个 RF 开关安装在单独的屏蔽外壳中,并串联起来。尤其是在 >10 GHz 的情况下,RF 开关、屏蔽外壳和放大器的价格可能会非常昂贵。

传统上,设计宽带 RF 信号源也是一个挑战。通常需要多个混频器、振荡器、滤波器和倍频器才能在整个 VNA 频率范围内实现高质量的信号。但是,现在有一些廉价的 PLL 芯片,带有集成的 VCO 阵列,可以生成非常宽频率范围内的信号。例如,LMX2594 是一个 10 MHz 至 15 GHz 的 RF 信号源,采用单封装,大批量购买时价格为 38 美元。

使用集成的锁相环(PLL)IC 进行源信号生成,可以消除端口开关,而是为每个端口提供单独的信号源。这既经济高效,又简化了实现隔离要求的过程。

缺点是,用于源功率电平控制的可变衰减器和用于滤波谐波的滤波器组需要为每个端口复制。但是,如果可以接受低可调源功率范围,则可以移除外部可变衰减器,而改用 PLL 芯片的内部功率调节功能。LMX2594 的输出功率可以调节约 10 dB。

如果可以接受谐波,也可以移除滤波器组。理想情况下,在测量线性设备时,谐波不应影响 S 参数测量。但是,在实践中,接收器中可能存在一些非线性,导致谐波混合到基频。包含滤波器可以稍微提高测量质量。

在查看了 15 GHz 的可变衰减器和 RF 开关的价格后,我决定我可以接受谐波和低输出功率调节范围。

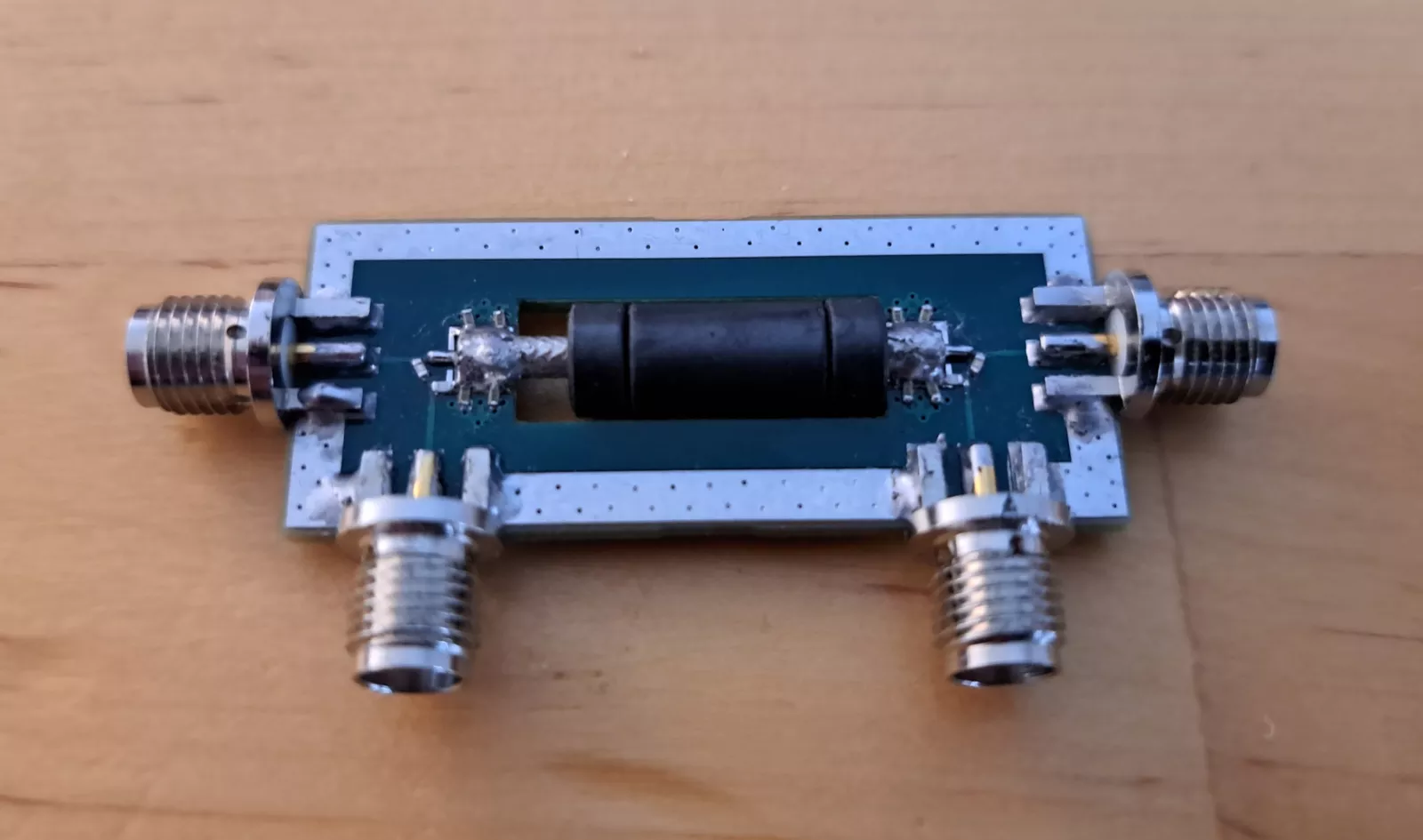

定向耦合器

VNA 需要定向耦合器来采样两个端口的入射波和反射波。这些耦合器还应在 10 MHz 至 15 GHz 的频率范围内工作,具有良好的方向性和低损耗。许多商用 VNA 中使用的标准定向耦合器是电阻式定向电桥。它需要一个平衡-不平衡转换器,在这种情况下,该转换器由一根被铁氧体磁珠包围的同轴电缆来实现,以将其工作范围扩展到低频。

在我之前的 VNA 中,我使用了类似的定向耦合器,但它只有一个耦合端口。我意识到,在此应用中,当需要两个耦合器来采样反向波和正向波时,可以将两个耦合器背靠背放置,共享同一根同轴电缆平衡-不平衡转换器,这使其更小。

定向耦合器分线 PCB。

定向耦合器分线 PCB。

我制作了一个耦合器的分线 PCB,以便可以测量它,因为它的性能对于 VNA 非常重要。PCB 材料是 FR4,它在高频下损耗很大,但是合适的 RF 材料会太昂贵。

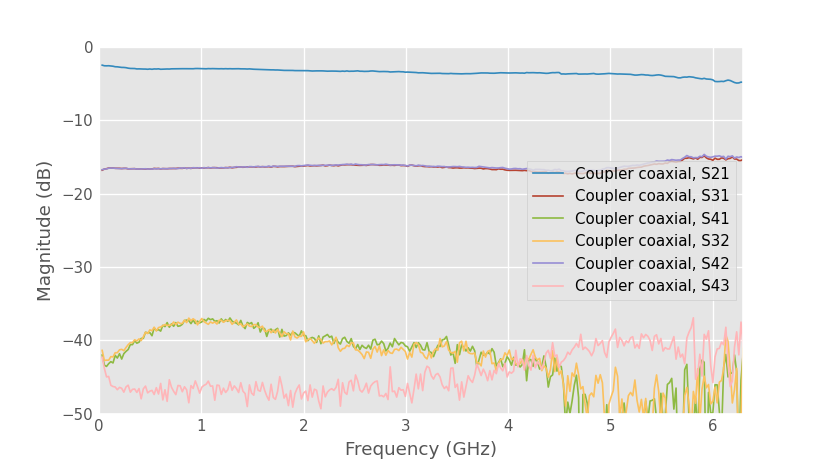

耦合器的测量 S 参数。端口 1 和 2 是直通路径,端口 3 和 4 是耦合端口。

耦合器的测量 S 参数。端口 1 和 2 是直通路径,端口 3 和 4 是耦合端口。

我用我之前的 6 GHz VNA 测量了耦合器,性能看起来不错。它是一个四端口,但这不成问题,只需要进行多次测量。损耗在低频时为 3 dB,在 6 GHz 时为 5 dB。方向性约为 20 dB,这很好,但可以通过稍微调整电阻值来改善。耦合端口之间的隔离是可以接受的,并且共享平衡-不平衡转换器似乎没有问题。

接收器

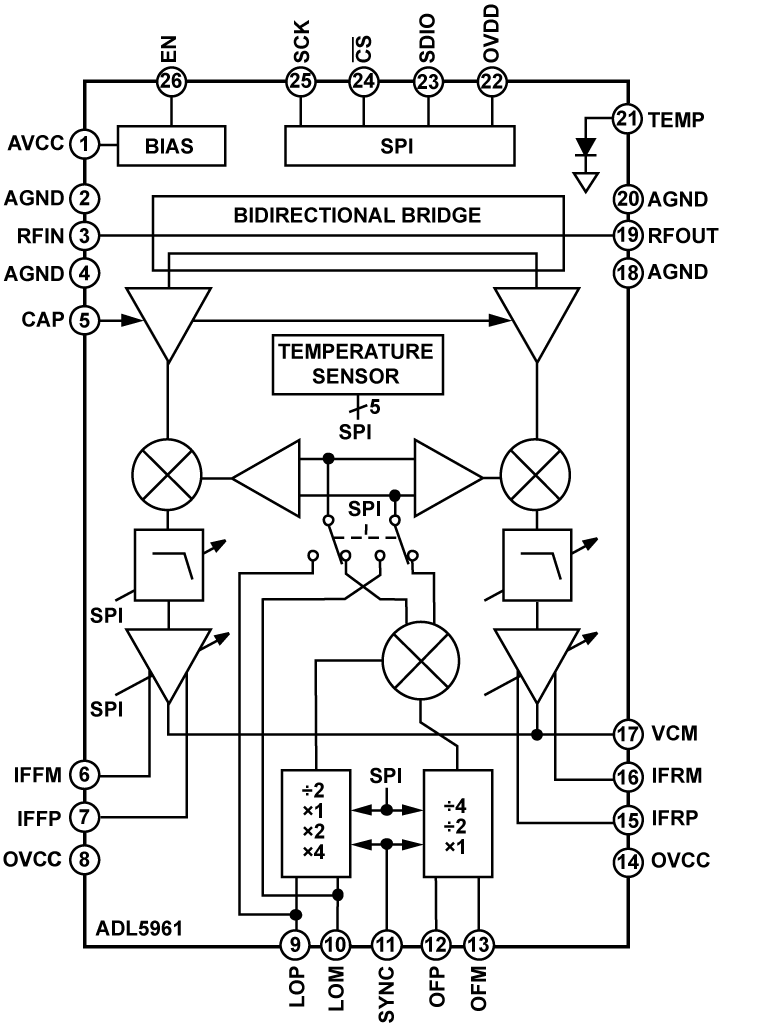

ADL5961 框图。如果不是价格问题,这将是 VNA 的理想接收器。它集成了定向耦合器,甚至包括 LO 分频器和倍频器。

ADL5961 框图。如果不是价格问题,这将是 VNA 的理想接收器。它集成了定向耦合器,甚至包括 LO 分频器和倍频器。

接收器需要先对来自定向耦合器的 RF 信号进行下变频,然后使用 ADC 对其进行采样。事实证明,寻找宽带混频器是有问题的。ADL5961 将是一个理想的选择,因为它额定频率为 10 MHz 至 20 GHz,专为 VNA 应用而设计,甚至在芯片上包含一个定向耦合器。缺点是单个芯片的价格为 200 美元,其中两个(每个端口一个)的价格将超过所有其他组件的总和。

其他选择非常有限。许多混频器在足够高的频率下都能工作,但几乎所有混频器也都具有很高的最低频率。我可以为低频和高频切换两个混频器,但这将花费太多。即使在规格之外运行,一些混频器也可能在低频下具有足够的转换增益,但我不希望单独测试它们。另一个选择是使用二极管制作我自己的混频器,但这将需要大量的测试,并且生成的电路可能会比小型商用集成电路大得多。

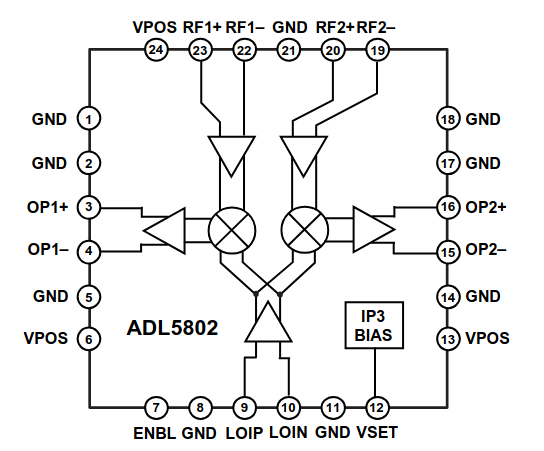

ADL5802 双通道混频器框图。

ADL5802 双通道混频器框图。

最后,我选择使用 ADL5802,它的额定频率仅为 100 MHz 至 6 GHz。不幸的是,当其他所有东西都能正常工作时,这会限制高频的性能。但是,我没有看到其他廉价的选择。它的主要优点是它很便宜(大批量购买时每个 12 美元),并且它在一个封装中具有两个混频器,从而进一步降低了成本。我选择使用它的原因是它确实有一些在 8 GHz 时列出的性能数据,这表明它的转换增益比在 6 GHz 时低 5 dB。即使它在 8 GHz 以上不能很好地工作,这也应该足够好,因为我目前主要在 7 GHz 以下的频率下工作。

ADC

模数转换器 (ADC) 的动态范围至关重要,因为它通常限制了接收器的动态范围。混频器输出可以在噪声本底(大约 -160 dBm/Hz)到大约 +10 dBm 之间变化,这是 1 dB 压缩点的最大输入功率。这个宽动态范围超过了大多数普通 ADC 可以处理的范围。ADC 的动态范围取决于单个样本中的噪声和平均的样本数。当平均多个样本时,更快的低比特 ADC 可能比慢的多比特 ADC 更准确。

混频器输出频率应至少为几百 kHz,以最大程度地减少相位噪声和 1/f 噪声的影响。更高的中频 (IF) 可以缩短测量时间,因为必须对至少几个 IF 周期进行采样。还应为 ADC 的抗混叠滤波器的滚降留出一些裕量。更高的采样率还可以提高频谱分析仪的性能,但会增加 ADC 的成本。

ADC 动态范围的关键性能指标是噪声频谱密度 (NSD)。许多 ADC 报告的是单个样本的信噪比 (SNR)。使用采样率,可以按以下方式计算 NSD:

NSD=−SNR−10log10(fs/2)

其中 fs 是采样率。通常约为 -140 至 -160 dBFS/Hz(相对于 1 Hz 带宽下 ADC 满量程输入的噪声本底分贝)。实际上,此数字告诉您作为测量长度函数的 ADC 输出的 FFT 噪声本底。例如,对于 0.1 秒的测量时间和 -140 dBFs/Hz 的 NSD,FFT 噪声本底低于满量程非削波输入 -130 dB。

我选择使用的 ADC 是 AD9238,它的最大采样频率为 40 MHz,NSD 为 -143 dBFs/Hz。由于 ADC 的动态范围小于混频器输出的动态范围,因此高输入会导致 ADC 饱和,或者 ADC 的噪声本底高于混频器的噪声本底。在这种情况下,两者兼而有之。

对于 -143 dBFs/Hz 的 NSD,如果在 ADC 输入端,入射波功率为 -10 dBFs 电平,则 S21 测量的动态范围最多为 133 dBFs/Hz,因为它被计算为端口 2 接收功率与端口 1 入射功率之比。使用 10 Hz IF 带宽,S21 测量将具有 -123 dB 的噪声本底。如果源功率较低,则入射功率会降低,并且 S21 噪声本底会增加。

如果成本不是问题,则有更好的选择。例如,AD9650(105 MHz 版本)的 NSD 为 -160 dBFs/Hz。它将使动态范围增加约 17 dB。它也贵了十倍,因此性能并非来之不易。

FPGA

快速采样率 ADC 需要 FPGA 来处理它们产生的大量数据。同一个 FPGA 还可以处理所有 DSP 和 I/O 控制功能,从而避免了添加单独的微控制器的需要。

FPGA 内部所需的数字信号处理非常简单。来自四个接收器中的每一个的输入信号是以几 MHz 频率的信号。它乘以相同频率信号的正弦和余弦,以获得零频率的 I 和 Q 输出信号,这些信号被求和。在采样周期结束时,这些 I 和 Q 累积和除以求和的样本数,以获得平均值。这等于仅计算傅里叶变换的单个 bin,并且是计算已知频率信号的幅度和相位的最佳方式。

FPGA 上的其余逻辑是时序、切换 I/O 信号以及与 PC 通信。所有逻辑和校准都在 PC 上实现,因为在那里更容易操作。

PCB

部分组装的 VNA PCB。

部分组装的 VNA PCB。

PCB 有 6 层,由 FR4 材料制成。FR4 在此应用中很好,因为从信号源到输出端口的距离很短,并且没有任何敏感电路,例如对基板材料变化敏感的分布式滤波器。

为了获得良好的隔离,RF 外壳是必不可少的,并且需要在 PCB 上安装孔和接触表面。隔离是我之前 VNA 的最大问题,我尽一切努力确保这次泄漏信号低于噪声本底。由于高频率,所有 RF 信号都路由到顶层,需要在屏蔽中路由通道以通过信号通过不同的外壳。

组装好的 VNA。

组装好的 VNA。

我订购了组装好的 PCB,但我不得不自己组装一些组件,例如混频器、SMA 连接器和耦合器。当考虑大规模生产时,耦合器尤其棘手,因为它们需要手动切割同轴电缆,将铁氧体磁珠插入其中,然后将其焊接到 PCB 上。在这种情况下,当我只为自己制作一个 PCB 时,这不是问题,但是这对于大规模制造来说将是困难的。

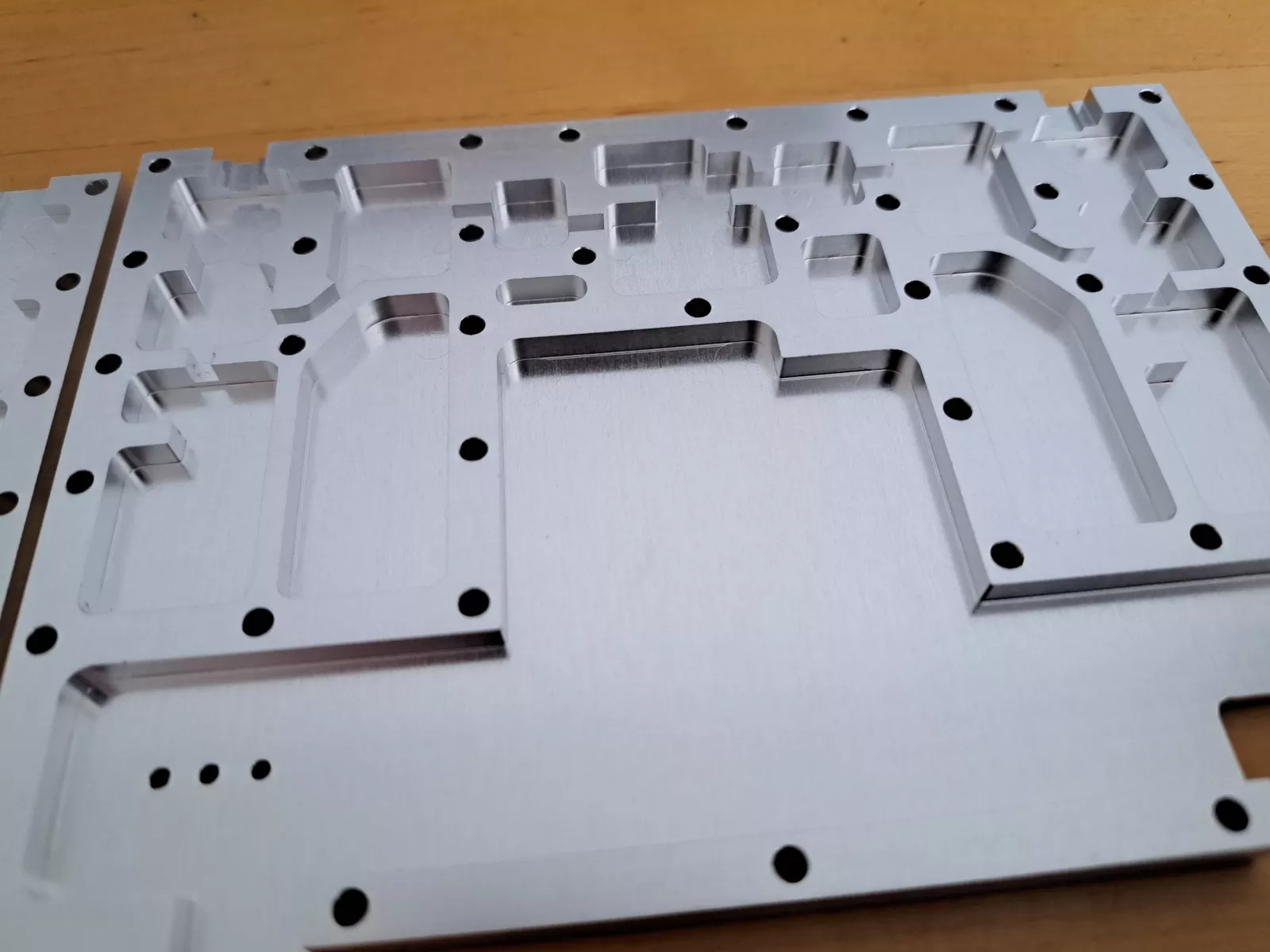

CNC 加工外壳

CNC 加工外壳,上半部分。

CNC 加工外壳,上半部分。

我首先制作了一个衬有铝箔的 3D 打印外壳,用于测试电子设备并确保机械设计适合 PCB。在我弄清楚如何使铝箔衬里没有撕裂后,它具有相当好的隔离效果。CNC 加工外壳的稳定性和热性能应该更好,所以我订购了用铝加工的相同设计。

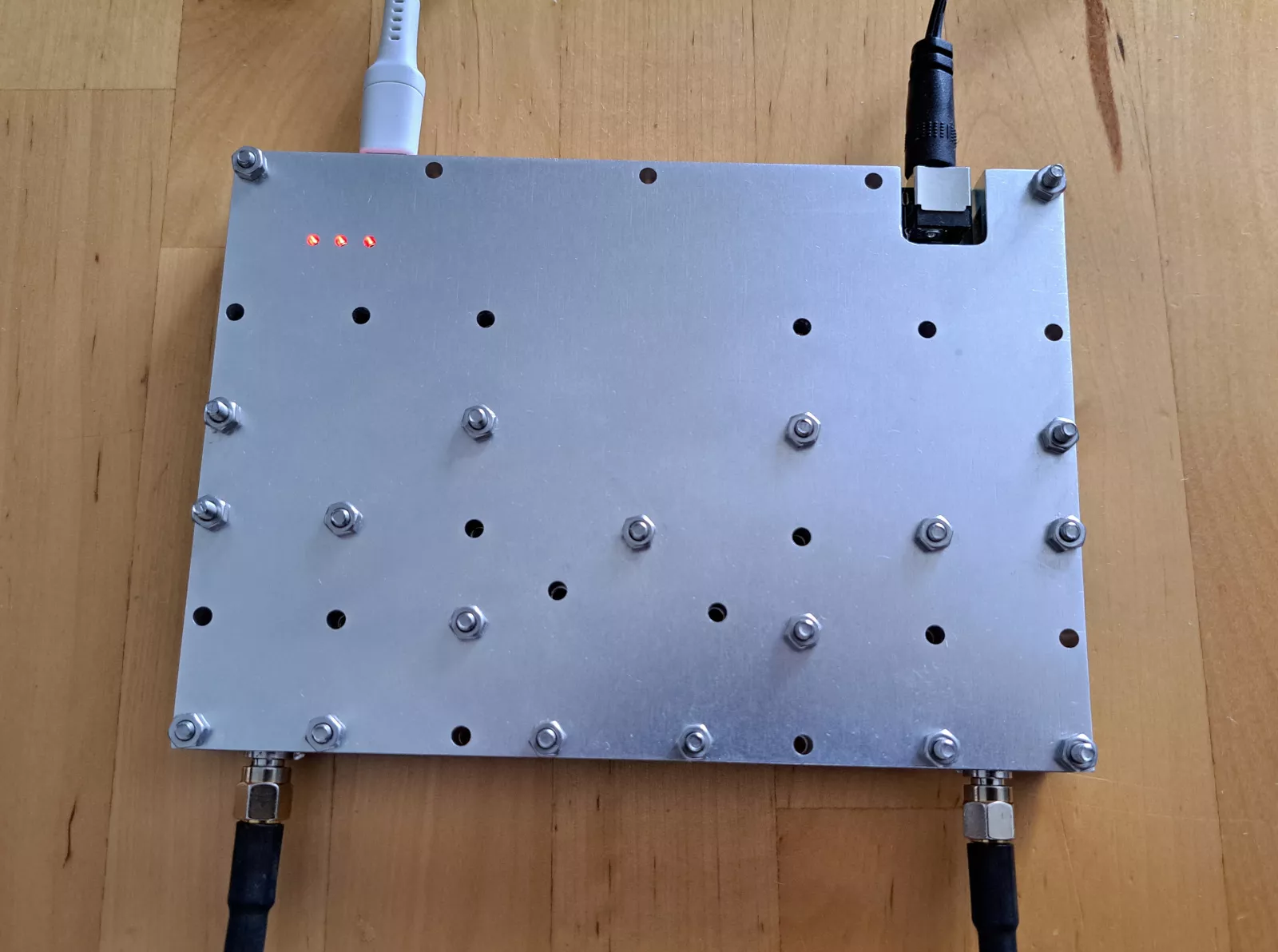

带有铝制外壳的 VNA。

带有铝制外壳的 VNA。

外壳由上下两部分组成,PCB 夹在它们之间。我将其设计为简单,以便可以在 3 轴 CNC 机床上一次性制造,而无需任何螺纹。外壳的成本为 75 美元,运费为 37 美元,税金为 29 美元。对于一块相当大的铝来说还不错。

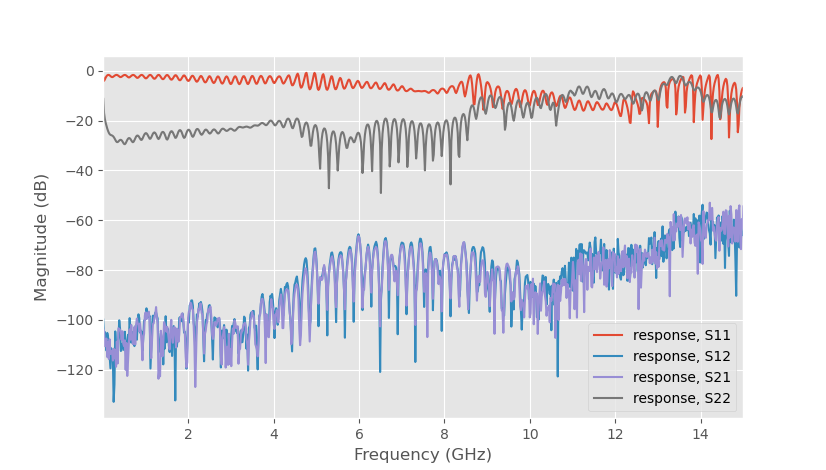

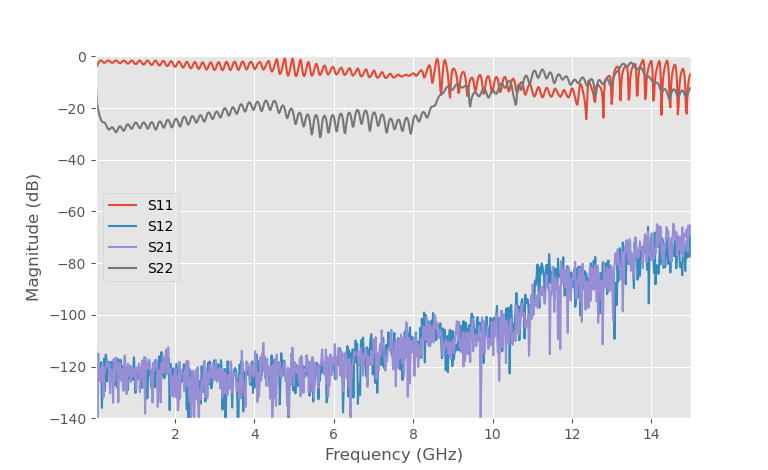

端口 1 短路,端口 2 负载的未校正 S 参数。200 Hz IF 带宽。

端口 1 短路,端口 2 负载的未校正 S 参数。200 Hz IF 带宽。

当我第一次组装时,CNC 加工外壳的泄漏高得惊人。在 6 GHz 时,未校正的 S21 高于 -70 dB。罪魁祸首是边缘发射 SMA 连接器和铝制外壳之间的间隙。连接器和外壳之间的间隙非常小,小于 1 毫米,但它作为天线的工作效果非常好,以至于与另一个端口的耦合约为 -70 dB。

用于密封 SMA 连接器和铝制外壳之间间隙的焊锡丝和铝箔。

用于密封 SMA 连接器和铝制外壳之间间隙的焊锡丝和铝箔。

我使用铝箔堵住了底部外壳和连接器之间的间隙。放置在 PCB 下面的一个小折叠的箔片可以很好地压缩并提供良好的 RF 密封。上半部分无法使用相同的方法,因为它会使信号导体短路。我改用一小块焊锡丝来密封上半部分的间隙。

当我第一次设计 VNA 时,我就知道这个连接器间隙可能是一个问题,但我决定这样做,因为使用隔板 SMA 连接器(整个连接器穿过外壳)的替代方法太麻烦了。隔板连接器需要在外壳中以与当前加工方向成 90 度角的方向开孔和螺纹。隔板连接器还需要在将 PCB 安装在外壳中时将其焊接到 PCB 上,这使得原型制作不方便。

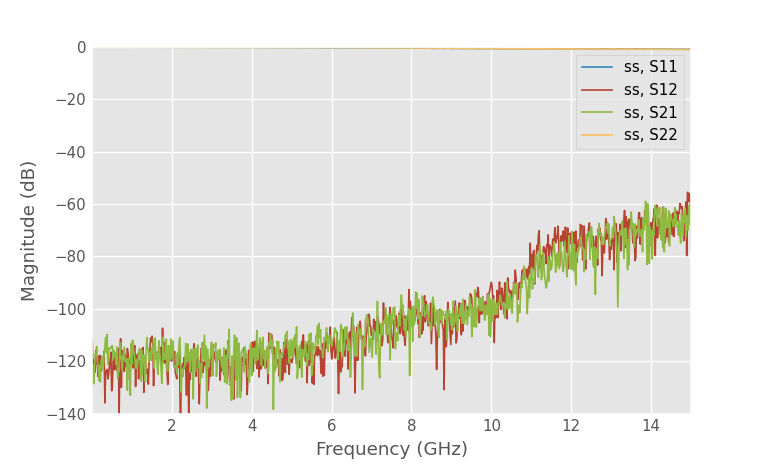

端口 1 短路,端口 2 负载且带有 EM 垫片的未校正 S 参数。10 Hz IF 带宽。

端口 1 短路,端口 2 负载且带有 EM 垫片的未校正 S 参数。10 Hz IF 带宽。

堵住间隙后,隔离效果更好,即使使用非常低的 10 Hz IF 带宽(每个频率点 0.1 秒的测量时间),在所有频率下泄漏都低于噪声本底。

噪声本底随着源频率的升高而增加。这是因为混频器的转换增益在 6 GHz 以上会降低。动态范围在高达约 10 GHz 的频率下仍然非常好,但在此之后开始迅速下降。虽然在低频下动态范围为 120 dB,但在 15 GHz 下动态范围小于 70 dB。

两个端口 1 和端口 2 都短路的校准 S 参数。10 Hz IF 带宽。

两个端口 1 和端口 2 都短路的校准 S 参数。10 Hz IF 带宽。

校准后,由于需要校准掉的损耗,高频的动态范围略低,但由于定向耦合器仍以可接受的性能工作,因此差异不大。虽然高频的较低动态范围可能不足以进行精确测量,但它仍然对许多基本测量有用。

谐波混频

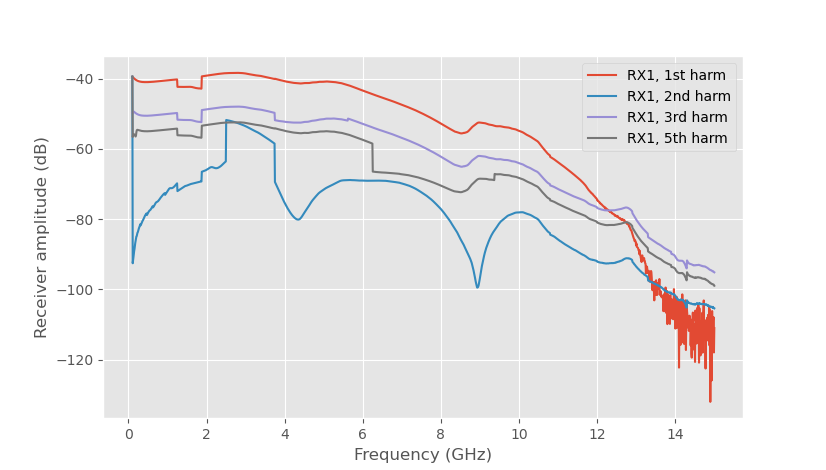

在不同 LO 谐波下的参考接收器测量(任意刻度)。

在不同 LO 谐波下的参考接收器测量(任意刻度)。

混频器额定工作频率仅高达 6 GHz,并且具有集成的 LO 放大器。在足够高的频率下,LO 放大器的输出功率不足以驱动混频器内核。如果以例如所需频率的 1/3 驱动 LO,则基频应该足够高,仍然可以通过集成的 LO 放大器,并且还应该有一些由 LO 的三次谐波引起的谐波混频产品。

我将源从 0.1 GHz 扫频到 15 GHz,LO 设置为不同的谐波。上图显示了参考接收器功率(任意刻度)的结果。结果是混频器输出的大小,它与耦合到参考接收器的源功率和混频器的转换增益成正比,因此该测量不仅测量混频器。正如预期的那样,基频导致混频器工作范围内的最高转换增益。在 10 GHz 时,IF 信号低约 15 dB,这仍然可以接受,但在此之上,它开始迅速下降。输出也变得非常嘈杂,可能是由于 LO 驱动功率太弱。在 12 GHz 左右,使用 1/3 频率的 LO 进行三次谐波混频会导致更高的输出功率。LO 的其他谐波(而不是 1 或 3)会导致较低的转换增益。

当输出分频器值设置为 6 时,LMX2594 芯片的输出功率似乎在 1.25 GHz 到 1.875 GHz 之间有一个 2 dB 的下降。由于源功率较低,因此所有迹线都可以在该频率范围内看到此下降。由于 LO 源功率的原因,在不同 LO 谐波的较高频率下也可以看到相同的效果。

一些 VNA 使用类似的源谐波技巧来扩展最大频率范围。例如,为了测量 20 GHz 的 S 参数,将源设置为 10 GHz,并将信号的二次谐波用作测试信号。LO 将设置为 (20 GHz + IF 频率)/3 = 6.67 GHz,用于 LO 的三次谐波。但是,这种方法不能用于测量任何稍微非线性的设备,因为设备的非线性会导致谐波由于仍然存在的强基频信号而发生变化。同样,接收器的非线性可能会导致问题。用谐波驱动混频器 LO 不会遇到相同的问题。

稳定性

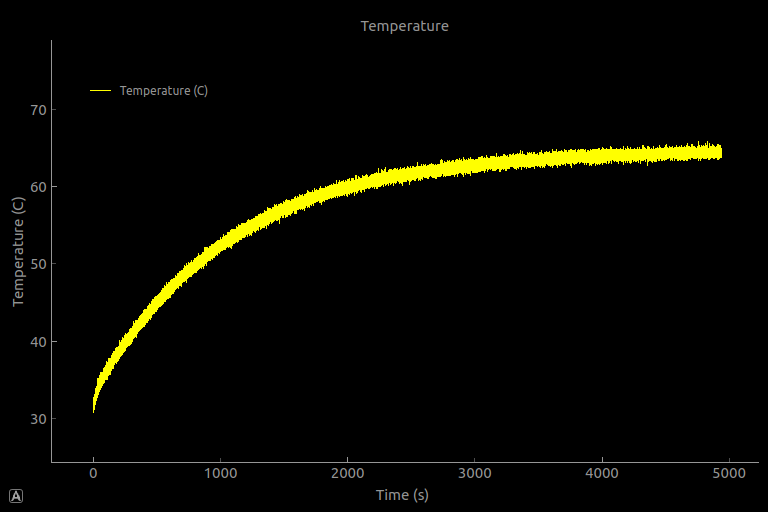

FPGA 的温度。

FPGA 的温度。

板确实变得很热,我估计它会消耗约 10 瓦的功率。FPGA 的内部温度传感器指示管芯温度为 64 摄氏度(147 华氏度)。外壳摸起来也很不舒服。达到平衡温度大约需要 1 小时。

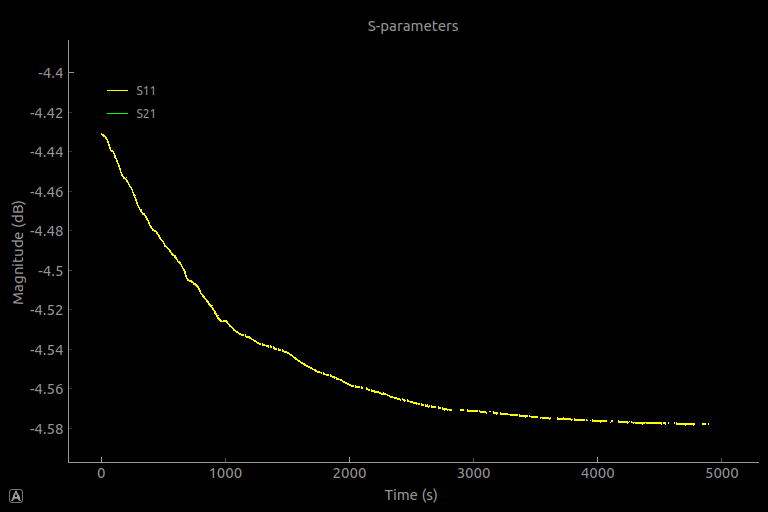

当 VNA 预热时,6 GHz 时短路的未校正 S11。

当 VNA 预热时,6 GHz 时短路的未校正 S11。

温度会对测量的 S 参数产生影响。对于端口 1 短路的情况,在 6 GHz 测量的未校正 S 参数从室温下的 -4.43 dB 变为温暖时的 -4.58 dB(包括 VNA 内部损耗和外部 0.5 米长的 SMA 电缆损耗)。源功率应在高温下下降,但由于 S11 是一个比率,因此它应该抵消。入射波和反射波混频器位于同一封装中,彼此匹配良好,并且温度相同,因此它们的转换增益变化也应该抵消。这只剩下耦合器作为漂移的可能原因。

热漂移的一个可能原因是 FR4 PCB 介电常数和损耗角正切可能具有较大的温度变化。铜电阻也会随着温度的升高而增加。同轴电缆的损耗在 60 摄氏度时比在室温下大约大 7%,并且 PCB 上的微带线的损耗可能会更大。入射波和反射波之间的区别在于入射波不通过耦合器,但反射波通过耦合器,因此预计随着温度的升高,由于耦合器的损耗增加,未校正的 S11 会略有降低。耦合器中的电阻也会随着温度的升高而略有变化。

我尝试使用耦合器分线板测量不同温度下耦合器损耗的变化,并使用热风枪加热它。我家里没有热室,因此测量精度很低,但我确实观察到当将其加热到摸起来很热的温度时,S21 发生了约 0.1 dB 的变化。

另一个温度效应是同轴电缆和 PCB 中的热膨胀,这主要影响相位。即使只有结果的幅度很重要,相位精度也很重要,因为相位用于校准。

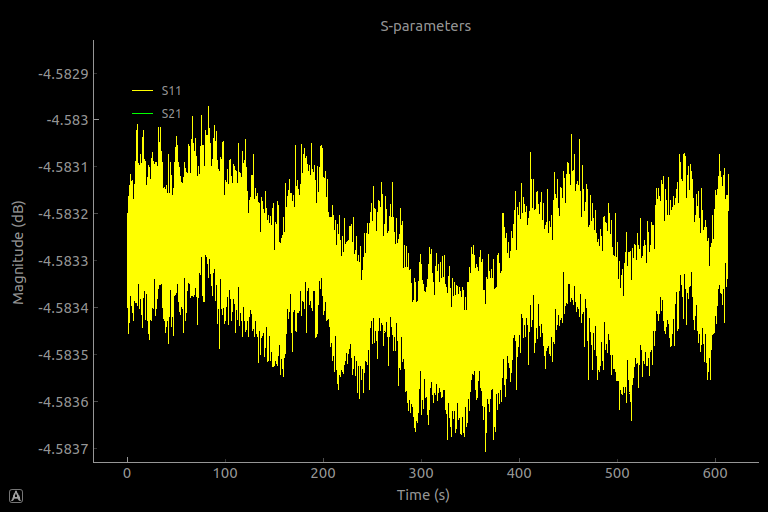

在 VNA 温度稳定后,6 GHz 时短路的未校正 S11。

在 VNA 温度稳定后,6 GHz 时短路的未校正 S11。

在温度稳定后,测量非常稳定。在 10 分钟的测量中,保持所有东西绝对静止,使用 100 Hz IF 带宽,未校正的短路 S11 测量中的漂移为 0.0001 dB RMS。单个测量中的噪声为 0.00006 dB RMS,仅受信噪比的限制。

您的浏览器不支持视频标签。 实际上,实现此精度具有挑战性。移动 SMA 电缆会将未校正的 S11 更改约 0.03 dB,并且当电缆返回到原始位置时,它不会返回到原始电平。弯曲电缆会导致更大的变化。连接器的可重复性,尤其是使用低质量 SMA 连接器时,也会影响测量精度。专业实验室因此使用昂贵的相位稳定电缆和精密连接器。

测量

自制的 VNA 校准套件。直通、短路、开路和 50 欧姆负载。

自制的 VNA 校准套件。直通、短路、开路和 50 欧姆负载。

对于校准套件,我使用的是我为之前的 VNA 制作的相同的自制短路、开路和负载。校准标准是用商用 VNA 测量的,该 VNA 使用高度精确的校准套件进行了校准,因此它们应该相当准确。直通是一个普通的 SMA 直通适配器,我没有任何关于它的测量数据,但这不成问题,因为我使用的是未知直通校准算法,顾名思义,该算法不需要已知的直通标准。

带通滤波器

6 GHz 带通滤波器。

6 GHz 带通滤波器。

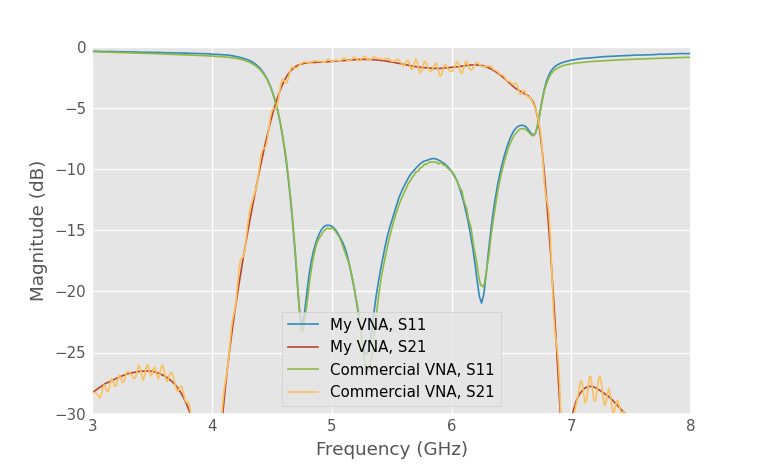

为了测试 VNA 的精度,我用我的 VNA 测量了一个 6 GHz 带通滤波器,该 VNA 使用自制的校准套件进行了校准。将结果与使用商用 VNA 拍摄的测量结果进行比较,该 VNA 使用适当的校准套件进行了校准。

带通滤波器具有安装在 FR4 PCB 上的 DEA165550BT-2230C2-H 陶瓷 6 GHz 带通滤波器。将铜片焊接在上面以创建一个外壳。

带通滤波器 S 参数比较。

带通滤波器 S 参数比较。

我的 VNA 测量的 S 参数与商用 VNA 的 S 参数非常匹配。我只绘制了 S21 和 S11 以使绘图更清晰,但是 S12 和 S22 也非常一致。

带通滤波器 S 参数比较,通带细节。

带通滤波器 S 参数比较,通带细节。

放大通带后,我的 VNA 在 S21 中的迹线噪声比商用 VNA 少。商用 VNA 应该更准确,我怀疑这是由于 SOLT 校准中不准确的直通标准定义造成的。它已经足够旧,以至于没有内置的未知直通算法。忽略迹线噪声,测量的 S 参数以极高的精度一致。

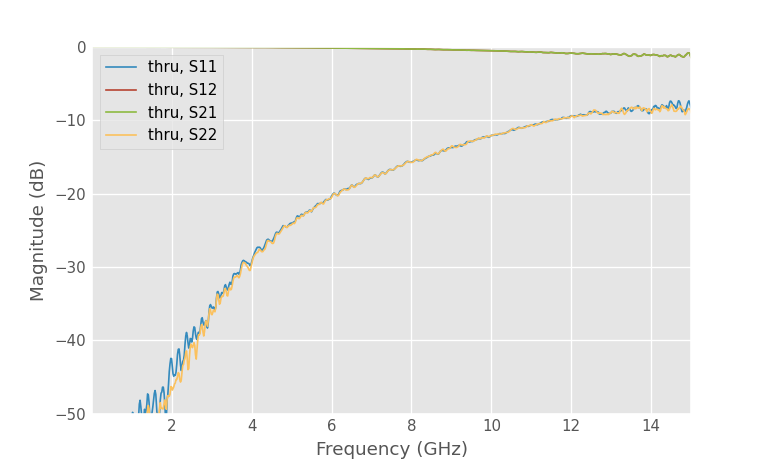

已求解的直通校准标准的 S 参数。

已求解的直通校准标准的 S 参数。

未知直通校准在校准期间求解直通 S 参数。绘制已求解的直通 S 参数,测量结果看起来质量很高,但是直通的性能看起来不是很好,并且绝对没有设计用于这些频率。在 15 GHz 时,匹配仅为 -8 dB。S21 迹线也非常干净 并且看起来非常合理,表明短路、开路和负载定义是正确的。

校准算法

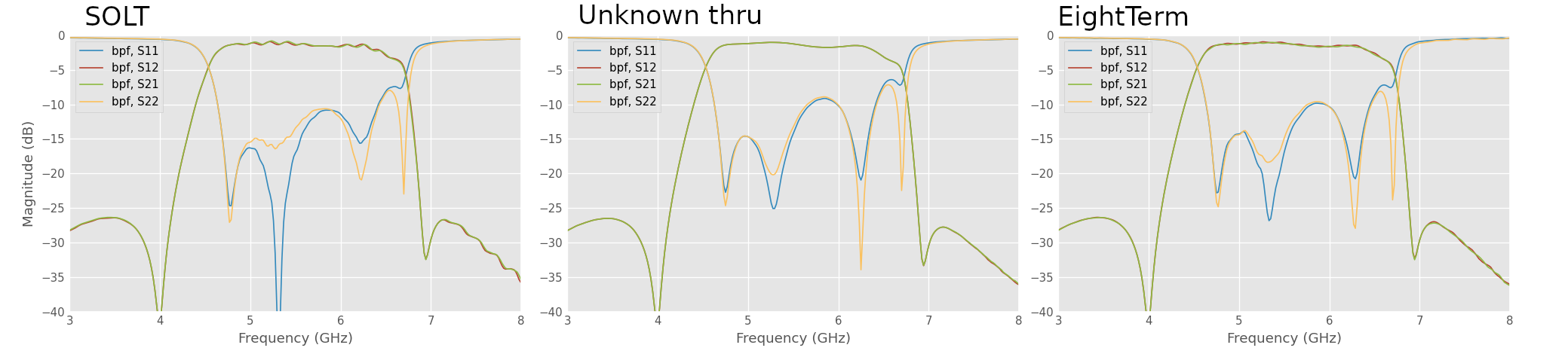

使用不同校准算法校准的相同测量。

使用不同校准算法校准的相同测量。

由于我保存了原始未校准的测量结果,因此可以在之后使用不同的校准算法进行校准。我将理想直通标准设置为长度为 65 ps 的 50 欧姆线路,在 4 GHz 时具有 0.1 dB 的线性衰减。这是一个简单的传输线模型,在低频时非常吻合,但是在较高频率下,损耗和匹配差异很大。延迟应该在整个频率范围内很好地匹配。

SOLT(短路-开路-负载-直通)校准算法是默认的经典 VNA 校准算法,也可以与三接收器 VNA 一起使用。它要求所有校准标准都已知精确。由于在这种情况下直通标准存在错误,因此已求解的 S 参数也存在错误。即使在 6 GHz 时直通的匹配为 -20 dB,但它造成的错误也远高于 VNA 的测量能力。

在校准到 SMA 连接器末端时,未知直通校准可能是最佳选择。它只需要知道短路、开路和负载标准,而直通标准可以完全未知,只要它是互易的 (S12=S21)。但是,此方法需要四接收器 VNA 来测量开关项。使用三接收器 VNA 无法进行此测量。当知道开关项时,它会将校准中需要求解的方程数量减少两个,从而允许放宽某些校准标准定义。