开放硬件以太网交换机项目,第一部分(Open Hardware Ethernet Switch Project, Part 1)

Switch 项目,第一部分

我长期进行的项目之一是开放硬件以太网交换机。这是推动我其他许多项目(例如 ngscopeclient 和高速探针)的关键动力之一。它也是让我进入高速数字设计的项目。

所以我觉得是时候开始一个系列,简要介绍一下目前的情况,我们是如何走到这一步的,以及接下来会发生什么。如果你在 Mastodon 上关注我,你可能已经零碎地看到过大部分内容,但我想把它们都集中在一个地方。

古代史:第一台交换机

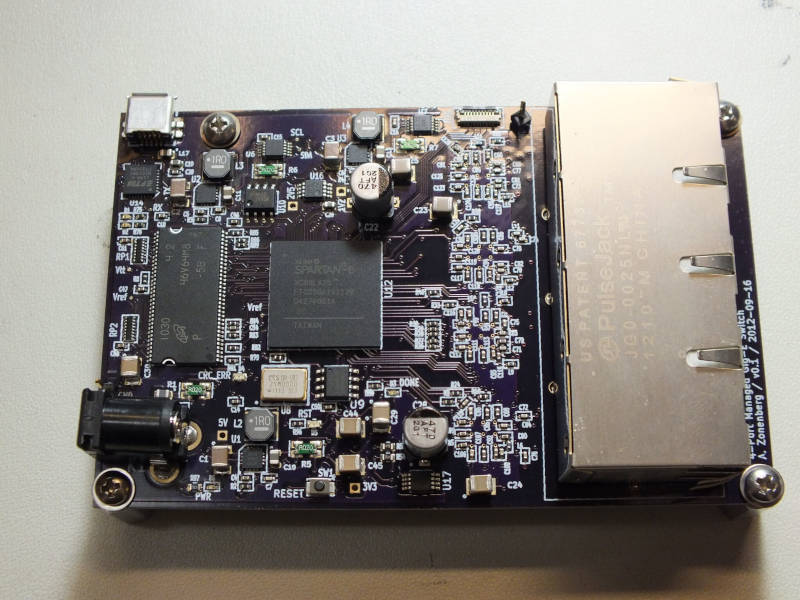

第一代交换机从来没有名字,它只是在我的 Subversion 仓库中被称为 “open-gig-switch” 或类似的东西(大约在 2012 年,当时我主要运行在 Git 上)。

我找不到任何适用于 OSH 项目的多端口千兆交换机 ASIC(即可以购买 1 个,数据手册不需要 NDA 等)。所以基于 FPGA 的从头设计似乎是唯一的选择。

这块板子突破了我很多的限制……我第一次使用开关电源而不是 LDO,我迄今为止最大、最复杂的板子,而且我想可能是我第一次使用 RGMII PHY(我之前使用过 Microchip ENC424J600,它是一个完整的 10/100 以太网 MAC + PHY,包括连接到并行总线或 SPI 接口的缓冲存储器)。

当时我最精密的测试设备是一台 100 MHz 的 Rigol DS1102D。所以我无法对以太网差分对甚至 250 MT/s 的 RGMII 线路进行信号完整性测量。

这个项目实际上并没有取得任何进展。我启动并运行了四个 PHY 中的三个,PHY #4 从未工作过(我不记得它是无法连接、无法传递数据还是什么)。我尝试重新焊接了很多东西,但从未使其正常工作。

我尝试用 3 个端口启动一个基本交换机,但很快意识到 15K LUT、<1 Mbit 的 BRAM 且没有外部 CPU 会使这项工作非常具有挑战性。XC6SLX25 不是一个大型 FPGA,添加 Xilinx DDR 控制器、一个软核 CPU 和三个 MAC 并没有为 fabric 留下多少空间。此外,我仍然是一个相对新手的 FPGA 开发者,还没有完全准备好应对这个项目。

所以这块板子最终走到了死胡同,但为接下来的事情奠定了基础。

过渡时期

第一次交换机的惨败告诉我,我需要更多的技能、更好的测试设备、更好的调试工具等等。

我当时还在读研究生,没有多少设备预算,但在攻读博士学位的过程中,我成了一名经验丰富的 RTL 工程师。我构建了几块带有以太网的板子,它们大部分都能正常工作。

但由于我买不起更好的示波器,也无法验证更快速度的 SI,所以我决定暂时搁置交换机项目。

2015 年我毕业了,找到了一份比我当研究生助教时收入高得多的工作。我的第一批采购之一是我的第一台 “真正的” 示波器,一台 350 MHz 的 Teledyne LeCroy WaveSurfer 3034。它实际上足够快,可以对 RGMII 进行 SI 工作和协议解码 100baseTX,但我梦想着更快的速度。

我知道我最终想在交换机上安装 10GbE,并且不指望很快就能买得起一台多 GHz 的示波器,所以我开始寻找其他方法来验证这些速度下的 SI。这让我走上了另一条理发之路,我开始设计一个名为 FREESAMPLE 的 10 GHz 采样示波器(从未完成,但我确实想有一天重温这个项目)。然后,当我意识到如果没有同样高带宽的探头来喂它,高速示波器将毫无用处时,这个项目就被搁置了。

你可能已经知道这个故事会走向何方。我的开放硬件 16 GHz 探头(可能值得单独写一篇或一系列文章)现在基本上已经完成,并且正在进行初步的 PVT 运行,希望我实际上可以批量生产它们并在未来几个月内提供给公众。

在理发这些 yaks 的过程中,我还买了一栋房子,花了一两年的时间来翻新它,得到了一个 Sonnet EM 求解器席位,在 eBay 上找到了一台价格低得惊人的 16 GHz 示波器(这使得 FREESAMPLE 的优先级降低了很多),用 OpenGL 加速重写了 “scopeclient” 为 “glscopeclient”,然后又用 Vulkan 重写为 “ngscopeclient”。我还为 10/100 baseTX、1000baseX、SGMII、QSGMII、10Gbase-R 和一些其他可能相关的协议创建了协议解码器。

我还开始为一系列网络设备构思路线图,这些设备都属于随机生成的伞形名称 LATENTx,使用颜色来表示子项目(大致受到 Lockheed HAVE BLUE 的启发)。最初的路线图要求 LATENTRED 成为千兆边缘交换机,LATENTORANGE 成为 10G 核心交换机,但我认为首先需要一个原型/技术演示平台。LATENTINFRARED 太长了,所以我选择了 LATENTPINK 作为名称。

LATENTPINK

最初的 LATENTRED 概念要求在三个 8 端口线卡上提供 24 个边缘端口(因为 3 的倍数便于使用 OSHPark 进行制造)。RGMII 将是一场路由噩梦,因为 24 条 RGMII 通道需要 288 个引脚(时钟、控制、4 位数据总线,乘以 2 表示 TX/RX 通道)加上 MDIO、复位等。所以我开始寻找引脚数更少的选项(GMII 需要 576 个引脚,甚至不在考虑之列,因为免费 Vivado 版本支持的 FPGA 没有超过 520 个 GPIO,而且任何更大的 FPGA 都会大大超出我的价格范围)。

显而易见的 “简单” 选项是 SGMII,它每个 TX 和 RX 需要一对差分线(4 个引脚)。这只需要 96 个引脚用于 24 个 PHY,并且无需担心并行总线时序约束(只需匹配每个差分对的 P/N)。所以我开始研究 TI DP83867。

但该项目已经拖延了足够长的时间,以至于当我准备为 LATENTPINK 制作硬件时,已经是 2023 年初了,并且出现了一个新的选择。Vitesse 此前一直在我的 “黑名单” 上,因为他们对开发人员不友好的做法(例如将最无聊的产品的数据手册锁定在 NDA 后面),但在 2015 年被 Microsemi 收购,然后在 2018 年被 Microchip 收购。作为其中的一部分,许多零件都被打开了,我认为他们应该因为表现良好而提前发布……这意味着他们的 12 端口 QSGMII PHY,VSC8512,现在可以考虑了。这将允许使用 24 个端口,仅需六个收发器链路(12 个差分对 / 24 个引脚),与 SGMII 相比大大减少。

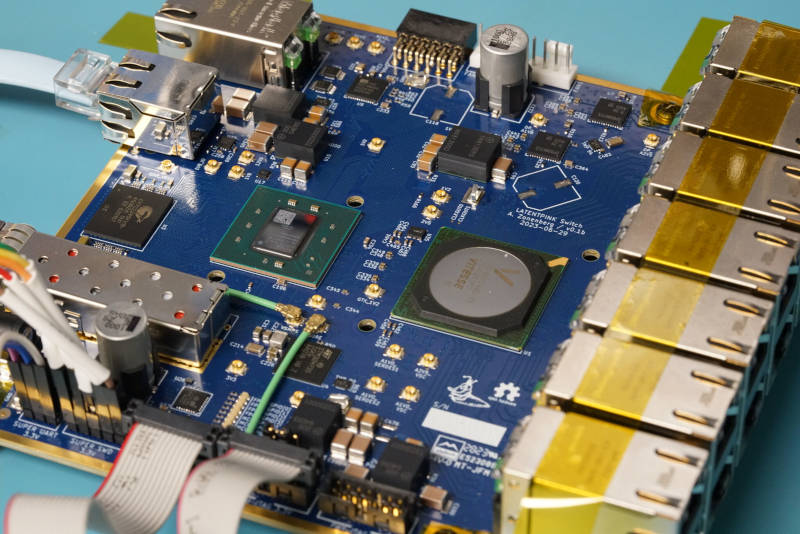

唯一的问题是,我以前从未与 QSGMII 合作过,并且 VSC8512 需要相当多的寄存器配置才能正常工作,所以我想稍微对冲一下风险。这导致了 LATENTPINK,它有一个 VSC8512 和两个 DP83867,总共有 14 个 1G 边缘端口,外加一个 10G SFP+ 上行链路和一个专用的 RGMII 管理端口(使用我久经考验的首选 PHY,KSZ9031RNX)用于 SSH 接口。

这是我的第二块 8 层板(第一个用于完全个人而非工作相关的项目),我第一次使用我现在随处可见的 Murata MYMGK 模块,也是我第一次使用 FPGA 收发器的设计之一。这也是我第一次尝试将 STM32H7 与 FPGA 配对(通过四路 SPI,因为我还没有了解到 H7 OCTOSPI 外设是多么的灾难,但这没关系,因为我只是在进行手动寄存器读取/写入,而不是尝试进行内存映射)。

我让 VSC8512 正常工作,MCU (缓慢地) 与 FPGA 通信,并使用该平台构建了我的 SSH 服务器和完整交换机需要的许多其他构建块。

LATENTPINK 板包含一个外部 QDR-II+ SRAM,它用作基于共享内存的交换 fabric 的数据包缓冲区。所有传入的数据包都被写入小的按端口 CDC FIFO,然后从这些 FIFO 中以循环方式弹出,并写入 QDR 的一个区域,该区域充当该端口的大型数据 FIFO。

在另一侧,转发引擎将循环选择一个源端口,然后读取 QDR FIFO 以从该端口弹出一个数据包。来自 QDR 的输出数据流然后被写入小的按端口出口队列,路由到所有这些队列,并且写入使能根据数据包要转发到的端口来控制。

此设计对控制平面使用自制寄存器结构,对数据平面使用另一个总线,两者都有问题。控制平面总线不支持任何类型的分布式解码,所以我不得不将所有寄存器逻辑放在一个地方,这需要将解码后的 SFR 路由到所有地方,而数据平面总线的 RX 为 32 位宽,10G TX 为 8 位宽,而 1G TX 为 8 位。这给设计增加了一些烦人的复杂性,并且非标准性质意味着我无法轻松地重用为其他项目编写的 FIFO 和其他块。

还有几个 PCB 错误,最值得注意的是一个错误的引脚排列,导致上面的端口行只能以 10/100 模式连接,直到我重新加工它们(考虑到必须在内部信号层(3 或 6,取决于端口)在一个相当狭窄的空间中执行交换,这是一个巨大的痛苦)。我验证了一个或两个端口上的修复,但没有重新加工整个板子。

总的来说,我把它弄到了可以正常工作的程度,它可以传递数据包,它有基于端口的 VLAN,并且可以解码入站 802.1q 标签(但不能在 trunk 端口上合成出站标签),然后我决定我已经证明了技术堆栈足够,可以构建真正的产品了。

接下来是什么?

LATENTPINK 的另一个主要发现是,至少按照我构建 fabric 的方式,XC7K160T 对于我的计划来说有点局促。虽然 14+1 端口设计很舒服,但我不认为很容易将 24+2 端口交换机装入其中。下一个最大的 7 系列部件 (XC7K325T) 在 FBG484 封装中不可用,所以我必须升级到 FFG676,但更令人烦恼的是,它不受免费 Vivado 版本的支持(需要 3000 美元的软件许可证),而且价格也贵得多(截至撰写本文时为 2260 美元 vs 435 美元)。

在这两个成本增加之间,我将花费 5000 美元的项目成本来跳到更大的 FPGA 并构建一个原型。我的长期目标是 96 个端口,所以要替换我所有的旧 Cisco 交换机,我将花费 3000 美元的软件 + 4x 2000 美元 = 11000 美元 更多 使用 325T 而不是 160T 构建整批交换机。这还只是低批量 8-10 层 PCB 制造、PHY 和 RJ45、底盘定制钣金工作等已经很高的成本之上。

不过,当我准备认真开始构建 LATENTRED 时,已经是 2024 年了。7 系列已经相当过时了,UltraScale 和 UltraScale+ 已经上市一段时间了。

我考虑围绕 Artix UltraScale+ 构建一个交换机,特别是最大的一个 - XCAU25P。截至撰写本文时,它的 FFVB676 封装 -1 速度等级售价低于 XC7K160T,为 380 美元。它的工艺节点更新两个(16 nm vs 28 nm),因此 fabric 快得多。而且在 141K LUT 时,它比 7K160T 的 101K 大得多,虽然远低于 7K325T 的 203K。其他规格也大多介于两者之间:12 个收发器 vs 8 个或 16 个等。但是它的块 RAM 很轻,10.5 Mb vs 11.7 或 16。我预计设计中需要大量的 FIFO,所以它会很快用完。

虽然我确实购买了一对 AU25P,但在我设计电路板之前,一位朋友提示我在 AliExpress 上发现了一批 Kintex UltraScale+,特别是 XCKU5P,每个仅售 55 美元。他测试了卖家的一个芯片,它们似乎是正品,虽然可能是从一些报废设备中回收/重新植球的。

这对项目的方向来说是一个重大的改变。XCKU5P 是免费 Vivado 许可证支持的最大的 FPGA,拥有 216K LUT(略大于 7K325T)、16 个收发器(与 325T 匹配)、16.9 Mb 的块 RAM(略大于 325T),外加另一个 18 Mb 的 UltraRAM,一种针对大型缓冲区进行优化新型大型 SRAM 块。这些收发器还支持 28 Gbps,从而支持 25/100G 以太网,而不仅仅是 10/40G。它们在商业温度等级下的零售价为 2972 美元,在工业等级下的零售价为 3350 美元(我得到的那些),所以我很高兴能以标价不到 2% 的价格获得它们!

唯一的问题是,随着这些新功能的出现,范围蔓延了。KU5P 上的 16 个收发器足以支持 12 条 QSGMII 通道(48 个 baseT 端口),外加一个 40/100G 上行链路或最多四个 10/25G 上行链路。而且似乎不利用如此昂贵的 FPGA 的全部功能,它以低廉的价格落入我的手中,这太可惜了。

LATENTRED

计划的硬件架构

新的 LATENTRED 概念是一个比最初计划强大得多的交换机。它将是一个 1U 交换机,带有两个 24 端口线卡(每个线卡两个 VSC8512)和双 10/25G SFP28 上行链路。

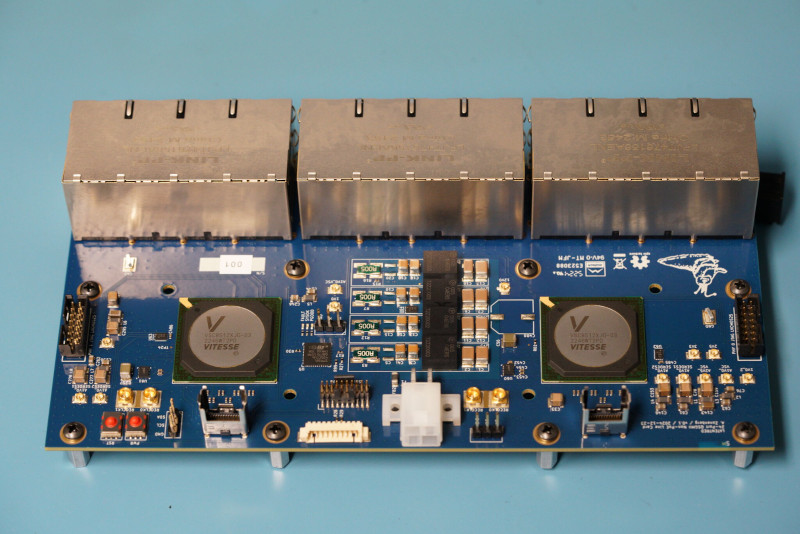

我最初考虑做四个 12 端口卡,但发现带有 AC 隔离中心抽头(VSC8512 的电压模式 MDI 驱动器需要)的 6 端口和 12 端口 magjacks 很难找到,而 LINK-PP 提供了 8 端口的。可被 8 和 12 整除的最小端口数是 24,并且一个 2x12 端口线卡刚好可以放入我的回流焊炉中。

整个交换机将由五个,可能六个,PCB 组成:

- 48 -> 12V 中间总线转换器

- 电源分配/切换板

- 两个 24 端口双 VSC8512 线卡

- 带有 XCKU5P、STM32H735、管理 PHY、串口等的交换引擎板。

- 可能会有一个单独的板,带有通过电缆连接到交换引擎的 SFP28 上行链路,具体取决于底盘机械布局是否比单片设计更容易

最初的概念还要求线卡通过刚性互连以菊花链样式连接(即所有 SGMII/QSGMII 通道进入一侧,每个线卡将从本地 PHY 分支几个通道,并将其他通道路由到另一侧)。这将导致长距离多千兆信号通过多个连接器在整个 19 英寸底盘宽度上运行,可能需要使用更高成本的低损耗基板。

不过,在浏览 Samtec 目录时,我发现了 AcceleRate 系列,更具体地说,是 AcceleRate Slim ARC6(电缆)/ ARF6(板)系列。这些是双轴差分互连,每根电缆有 8 到 24 个差分对,并且额定用于 32 Gbps NRZ 或 64 Gbps PAM4,因此插入损耗性能……对于 5 Gbps QSGMII 链路来说,只是稍微过头了。一根八对电缆可以处理 VSC8512 上三个 QSGMII 通道所需的六对,并留出两个额外的通道。

这种 “flyover” 风格互连的最大优点是不需要低损耗 PCB 材料或将大量差分对长距离路由,这会与其他路由冲突。只需将几个连接器靠近 BGA 放置,并将电路板的其余区域留给其他东西即可。

ARC6 也足够好,如果这样可以使底盘布局更容易,我可以使用它们作为远程 SFP28 连接器的 flyover。

当前硬件状态

IBC 已经设计并在其他项目中使用过,所以它已经完成了。我们可以忘记它,除了可能会对 3.3V buck 产生的纹波进行小的重新调整。但在目前的关税形势下,我并不着急(这是一个在中国 Multech 制造的 4L 2oz 板)。我有很多电路板和几个准备好的单元。

PDU 板已经完成。它没有太多内容:12V 进入左侧的 8 针连接器,12V 从右侧的 8 针连接器输出,12V 从底部的两个 4 针连接器输出。它还通过了来自 IBC 的 I2C 和 3.3V 待机导轨,同时从中分接,以运行可编程软负载切换和电压/电流监控。非常简单明了。我有三个板(一个已组装),所以为了获得我的 96 个端口,我只需要用一些我架子上有的零件组装第二个板。

线卡也已完成。我已经构建了一个,并且除了如果我没记错的话,端口 22 或 23 没有连接之外,它似乎工作正常。可能是焊接缺陷,因为左/右 PHY 布局基本上是复制粘贴的,但我还没有时间进行故障排除。我有十个 PCB,需要四个才能制作两个交换机;我将不得不从 LINK-PP 订购另外两个 8 端口 RJ45 来填充所有这些,但这离成为问题还有一段距离。

这是一个六层设计,使用廉价的 Shengyi S1000-2M 基板,因为 QSGMII 链路很短,而且其他一切都很慢。堆叠是 SGPPGS,所有以太网信号都在背面层上,并且一些 LED GPIO 在第 4 层电源灌注之间路由。与系统其余部分的连接是通过背面上的四个连接器进行的:4 针 Mini-Fit Jr 上的 12V 电源,跨两个 ARF6 连接器分割的六个 QSGMII 通道,以及提供对 PHY MDIO 总线、到大量系统健康传感器的 I2C 和到板载 STM32L431 管理微控制器(在当前固件中未使用)的 SPI 总线的 10 针 Molex PicoBlade,以防我想提供远程电源循环或类似的东西。

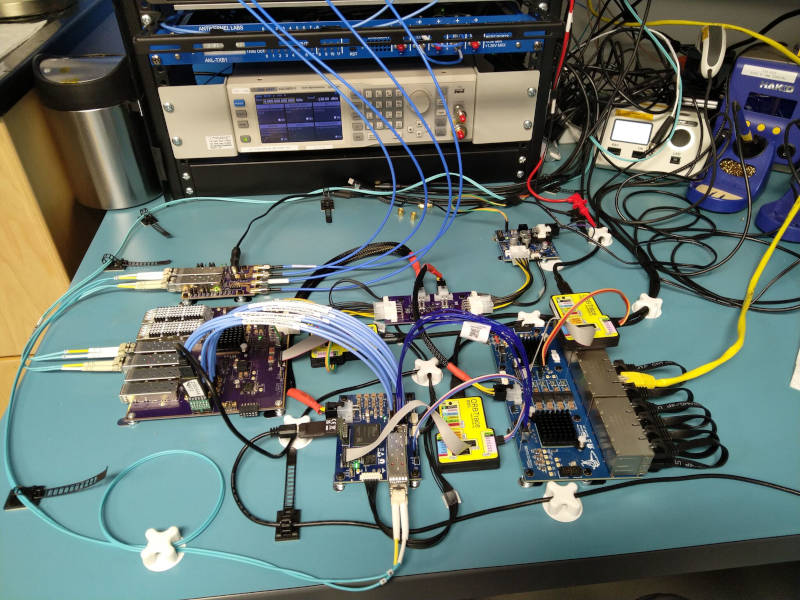

目前最大的缺失部分是交换引擎板本身。在短期内,我拼凑了一个类似子规模的测试设置,包括一个线卡、电源系统、我去年构建的 KU5P 开发板,以验证 55 美元的 AliExpress FPGA 不是砖头,以及一个带有 STM32H735 作为管理处理器的单独板。

无法将带有 FMC 的 STM32H735 直接路由到 FPGA,以启用我在 之前的文章 中描述的快速内存映射接口,因为开发板是在 OSHPark 4 层上构建的(我可能是第一个将 Kintex UltraScale+ 与所有分接出的收发器放在 4 层 PCB 上的人……关于此的文章将在稍后发布),所以我构建了一个带有 MCU、一个小型桥 FPGA (XC7A35T) 的小型扩展板,并通过 5 Gbps 串行链路将其连接到 KU+ 板。MCU 内存总线被桥接到 Artix 上的 APB,然后 Artix 通过一个简单的 PCIe 式协议(串行芯片到芯片总线,一旦我稍微调整了实现,可能会有自己的博客)将 APB 事务序列化,并返回到 Kintex 上的 APB。最终结果基本上与 MCU 直接连接到 Kintex 相同,但路径中的延迟略大。

粘合板还包含一个无源适配器电路,用于从 Kintex 板上的三组 SMPM 连接器桥接到 ARF6 连接器,这样我就可以分接出该 GTY 四通道与线卡通信。我还有第二块粘合板,可以将 QSFP28 桥接到 ARF6(使我能够使用线卡上的第二个 PHY),但我还没有时间组装它。

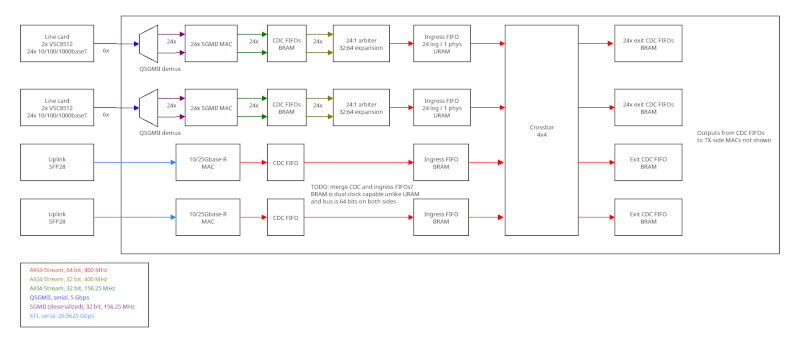

计划的交换引擎架构

我仍在研究实现的一些细节,但目前的总体计划是在 400 MHz 下的 4x4 64 位交叉开关。这将为每个通道提供 25.6 Gbps 的吞吐量,总共 102.4 Gbps。如果需要,由于时序困难,我理论上可以降低时钟频率到 390.625 MHz,但裕量的增加将很小,而且 400 是我从 25 MHz 合成时更方便的数字,而无需使用分数 N。

25G 上行链路将每个获得一个专用的交叉开关端口,而每个线卡也将获得一个(组合带宽 24 Gbps)。

4x4 交叉开关应该非常高效且性能方面,因为 4:1 多路复用器适合单个 LUT6。因此,一个 64 位 4:1 多路复用器是 64 个 LUT,而完整的交叉开关是 256 个 LUT,在关键路径中只有一层逻辑。决策逻辑将更加复杂,但如果需要,可以在较慢的时钟域中运行,因为转发数据包将需要多个周期。

在输入侧,将需要某种仲裁器和一些小的 FIFO,以获取 24 个 1 Gbps 流并将它们多路复用到单个 24 Gbps 流中,以及一些时钟域交叉块,这些块可能可以由相同的 FIFO 处理。如果需要更深的 FIFO,可以使用 UltraRAM。

在输出侧,每个端口将只有一个小的块 RAM 出口队列。25G 端口将直接将交叉开关出口流驱动到 FIFO 中,而 1G 线卡将有 24 个单独的出口队列(每个端口一个),使能由目标端口集(位掩码,允许广播/多播)控制。

当前门级电路状态

我已成功将现有的 10G MAC/PCS IP 移植到 AXI4-Stream,并在测试中运行良好。1G 几乎完成,RX 端的 AXI 转换已完成,但我尚未完成 TX。

我仍然需要编写一个 25G MAC/PCS,但这还有一段距离,我可以以 10G 运行上行链路,并很好地测试其余的交换机(在我无论如何都获得 25/100G 核心交换机之前,我实际上不会以 25G 点亮上行链路,这还有一段距离)。

LATENTPINK 中的 MAC 地址表可以在此设计中正常工作,无需修改,它具有足够的容量来满足我可以推送到 fabric 中的最大理论数据包数量。

我仍然必须构建 AXI4-Stream VLAN 标签插入/删除块,确定在什么时间点我想丢弃带有错误 FCS 的帧(可能是在它们被写入 URAM 入口 FIFO 的时候,但我还不确定),并实际进行所有集成。

结论

还有很多事情要做,但到目前为止,这是一个令人兴奋的项目,我期待看到它的发展方向。我不希望在 2026 年的某个时候(取决于制造/供应链延误和政治局势)在最终 PCB/机械设计上拥有一个完善的交换机,但我希望能在夏季的某个时候推送数据包。